介绍

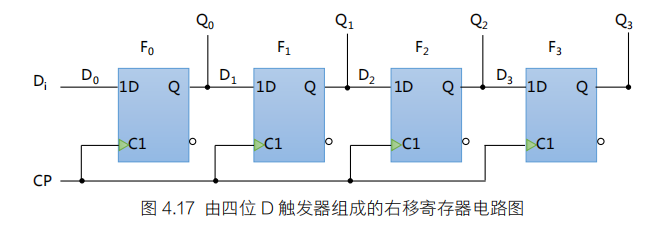

移位寄存器shift register是在相同时钟脉冲下级联的若干触发器,一个触发器的输出引脚q连接到下一个触发器的数据输入引脚d。 每一个时钟脉冲,寄存器阵列左移或右移一个bit。

串进并出

1. 左移

1位数据的串行输入,4位数据的并行输出。当时钟上升沿到达时,1位输入数据din进入qtemp的最低位,qtemp的低3位依次向左移动1位。在assign 赋值语句中,将qtemp连续赋值给dout,实现4位的数据并行输出。

| clk | din | qtemp |

| 1 | 1 | 0001 |

| 2 | 2 | 0012 |

| 3 | 3 | 0123 |

| 4 | 4 | 1234 |

input din;

output [3:0] dout;

reg [3:0] qtemp;

always @ (posedge CLK_50M or negedge RST_N)

begin

if(!RST_N)

qtemp <= 4'b0;

else

qtemp = {qtemp[2:0] , din};

end

assign dout = qtemp;2. 右移

当时钟上升沿到达时,1位输入数据din进入qtemp的最高位,qtemp的高3位依次向右移动1位。

qtemp <= {din,qtemp[3:1]};

| clk | din | qtemp |

| 1 | 1 | 1000 |

| 2 | 2 | 2100 |

| 3 | 3 | 3210 |

| 4 | 4 | 4321 |

循环移位

always@(posedge clk or negedegerst_n) begin

if(!rst_n) begin

qtemp <= 'd0;

end

else if(i_load) begin

qtemp <= din;

end

else begin

qtemp <= {qtemp[2 : 0], qtemp[3]};//循环左移

end

end

assign dout = qtemp;添加了一个信号,叫装载信号i_load,这个信号有效的时候,将输入din赋值给中间寄存器qtemp。这样才能实现每一个时钟上升沿来临时,都对输入左移一次。

用途

用来实现串并转换

最后

以上就是玩命大神最近收集整理的关于基于FPGA的移位寄存器介绍串进并出循环移位的全部内容,更多相关基于FPGA内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复