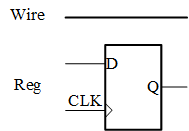

Verilog语法之多,初期学习只需要掌握常用的语法就OK了,基本就可以用Verilog HDL语言去描述逻辑电路了,今天学习两种数据类型:wire和reg。在数字电路中信号只有两种形态,一种是传输,通过线(wire),一种是存储,通过寄存器(reg)。因此,也就清楚wire和reg变量在Verilog HDL中的重要性了。下图是wire和reg变量的模型。

(1)wire(线型)变量:

①在物理结构上只是一根线,在Verilog HDL描述时,对线型变量赋值用assign即可,相对比较简单。

②wire是最常用的net型数据变量,net型数据相当于硬件电路中的各种物理连接,其特点是输出的值随输入值的变化而变化。net 型数据的值取决于驱动的值,对net型变量有两种驱动方式,一种方式是在结构描述中将其连接到一个门元件或模块的输出端;另一种方式是用持续赋值语句assign对其进行赋值。如果net型变量没有连接到驱动,则其值为高阻态z (trireg 除外)。Verilog 模块中的输入/输出信号在没有明确指定数据类型时都被默认为wire型。

| 类型 | 功能 | 可综合性 |

| wire,tri | 连线类型 | √ |

| wor, trior | 具有线或特性的多重驱动连线 | |

| wand, triand | 具有线与特性的多重驱动连线 | |

| tril, tri0 | 分别为上拉电阻和下拉电阻 | |

| supply1, supply0 | 分别为电源(逻辑1)和地(逻辑0) | √ |

| trireg | 具有电荷保持作用的连线,可用于电容的建模 |

③wire型变量定义:①wire a,b; //声明2个wire型变量a和b(一位)

②wire[7:0] databus; //databus(数据总线)的宽度是8位

wire[19:0] addrbus; //addrbus(地址总线)的宽度是20位

(2)reg(寄存器型)变量:

①在物理结构上相对比较麻烦,左端有一个输入端口 D,右端有一个输出端口 Q, 并且 reg 型存储数据需要在CLK(时钟)沿的控制下完成,在 Verilog HDL 描述时也相对麻烦。在对reg 型变量进行赋值时,必须在 always 块内完成。

②reg型变量是最常用的variable型变量,variable型变量必须放在过程语句(如initial、 always) 中,通过过程赋值语句赋值;在always、initial等过程块内被赋值的信号也必须定义成variable型。variable型变量(reg)并不意味着一定对应着硬件上的一个触发器或寄存器等存储元件,在综合器进行综合时,综合器会根据具体情况确定是映射成连线还是映射为存储元件(触发器或寄存器)。

| 类型 | 功能 | 可综合性 |

| reg | 常用寄存器型变量 | √ |

| integer | 32位带符号整型变量 | √ |

| real | 64位带符号实型变量 | |

| time | 64位无符号时间变量 |

③wire型变量定义:①reg a,b; //声明2个reg型变量a和b(一位)

②reg[7:0] out; //out的宽度是8位

部分转载:FPGA入门系列3--wire与reg

最后

以上就是无私乐曲最近收集整理的关于Verilog基本语法之wire和reg的全部内容,更多相关Verilog基本语法之wire和reg内容请搜索靠谱客的其他文章。

发表评论 取消回复