我是靠谱客的博主 踏实楼房,这篇文章主要介绍FPGA自学笔记(三)Verilog基本语法:always,case,assign,赋值FPGA自学笔记(三)Verilog基本语法一、always语句二、赋值语句三、case语句四、assign语句五、信号定义,现在分享给大家,希望可以做个参考。

FPGA自学笔记(三)Verilog基本语法

一、always语句

always 表示一直重复的活动。触发always语句方式:

- 延时(tb中): 要产生50MHz的时钟,所以周期为20ns

always #10 clk <= ~clk;

- 沿触发 : 此时always描述时序逻辑

always @(posedge sys_clk or negedge sys_rst_n) begin

...

end

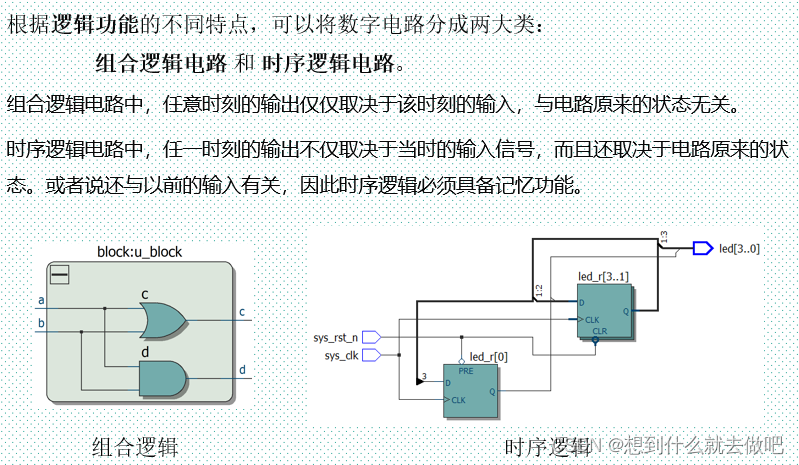

- 电平触发:此时always描述组合逻辑。PS:@(*)表示对后面语句块所有输入变量的变化都是敏感的

always @(a or b or c)begin

out = a ? b : c ;

end

always @(*)begin

...

end

二、赋值语句

1. 描述时序逻辑的always语句,用 非阻塞 赋值 <=,这种电路结构与触发沿有关;

2. 描述组合逻辑的always语句,用 阻塞 赋值 =,这种电路结构只与电平有关;

PS :不允许在多个always语句块中对同一个变量进行赋值

三、case语句

always @(posedge sys_clk or negedge sys_rst_n) begin

if(!sys_rst_n)

led <= 8'b0;

else begin

case (num)

4‘h0 : led <= 8'b1100_0000;

4‘h1 : led <= 8'b1111_1001;

...

default : led <= 8'b1100_0000;

endcase

end

end

四、assign语句

相当于一条连线,对wire型变量进行持续赋值,用阻塞赋值 =,描述组合逻辑

不可以放在always中,需要独立于模块写。

module breath_led(

input sys_clk,

input sys_rst_n,

output led

);

reg [15:0] period_cnt;

reg [15:0] duty_cycle;

assign led = (period_cnt >= duty_cycle) ? 1'b1 : 1'b0;

五、信号定义

对于每个模块的输入输出,有需要就定义,同一个信号在前后有了变化就定义。

比如,在按键控制led实验中,需要判断消除抖动后的按键信号,那就定义一个抖动消除后的输出信号呗

再比如:呼吸灯实验中,led亮的程度是变化的,所以也定义成一个变量inc_dec_flag,Inc由灭到亮为1,dec由亮到灭为0。

最后

以上就是踏实楼房最近收集整理的关于FPGA自学笔记(三)Verilog基本语法:always,case,assign,赋值FPGA自学笔记(三)Verilog基本语法一、always语句二、赋值语句三、case语句四、assign语句五、信号定义的全部内容,更多相关FPGA自学笔记(三)Verilog基本语法:always内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复