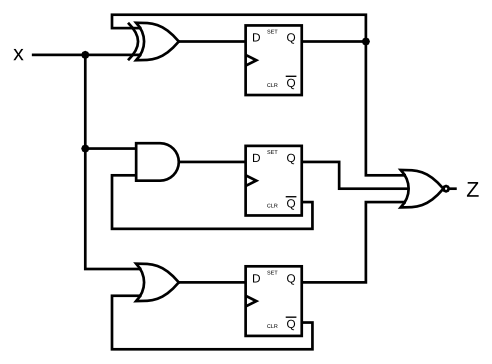

Given the finite state machine circuit as shown, assume that the D flip-flops are initially reset to zero before the machine begins.

Build this circuit.

其实本不应该记录这道题目但是自己踩坑了,所以还是记录下避免后续继续踩坑

在这道题目里有两个点要进行注意

- 初始化的时候是将Q输出全部置为0,那么我们可以将Q全部初始化为0,但是也可以将Z初始化为1,这是完全等价的

- 然后要注意到,程序里是需要使用阻塞赋值的,因为只有全部Q都到达最后一个逻辑或非的时候才能输出z,这点非常重要

题解如下

module top_module (

input clk,

input x,

output z

);

reg wire1,wire2,wire3;

initial z = 1;

always @(posedge clk)begin

wire1 = x^wire1;

wire2 = x&(~wire2);

wire3 = x|(~wire3);

z = ~(wire1|wire2|wire3);

end

endmodule

最后

以上就是真实人生最近收集整理的关于HDLBits Exams/ece241 2014 q4的全部内容,更多相关HDLBits内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复