题目:

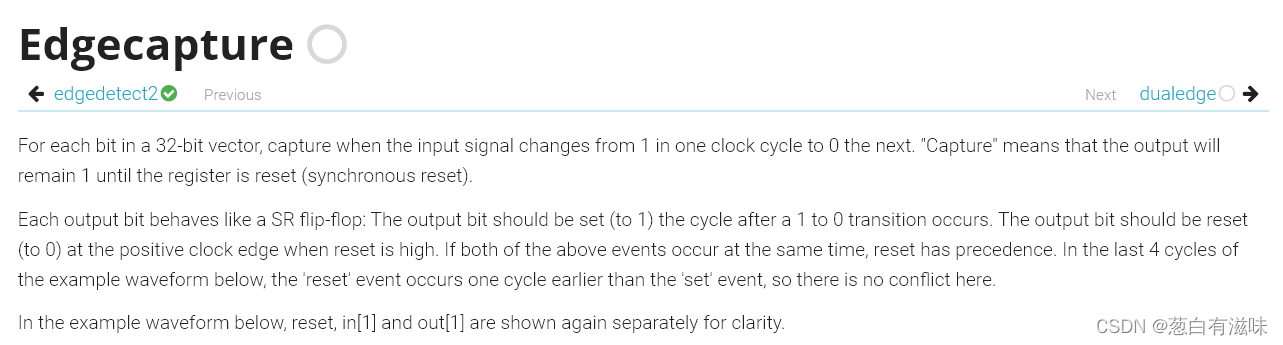

题目解释:对于单个bit而言,功能就是检测到1→0边沿后置输出为1并一直保持,直到reset时复位。

1→0检测=上一秒输入 & 下一秒输入取反

但这个结果不能直接赋给输出,因为如果下一个周期内输入不变,那么输出就会被赋0;

于是只能将1→0检测的结果中的1赋予输出,用或门即可实现,下面是正确答案。

module top_module (

input clk,

input reset,

input [31:0] in,

output [31:0] out

);

reg [31:0] in_temp;

always @ (posedge clk)

begin

in_temp <= in;

if (reset) out <= 0;

else

begin

// 错误写法in_temp <= in;

out <= (~in & in_temp) | out;

end

end

endmodule

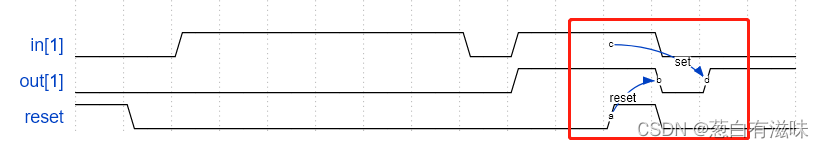

但这里有个坑, 如果将in_temp <= in;这一句写在else里面,reset有效时就不会执行保存输入到寄存器的动作,那么reset有效时的输入就会被丢弃。

如果深究一下,会发现如果这条语句写在外面,那么reset有效时,输入in也被正常存储了。不过对于上图标红的部分无所谓,因为输入在reset有效的时钟上升沿没有变化,所以in_temp无论是否采集reset有效期内in,in_temp都是1,图中这个边沿都能检测到。如果reset时间长一点,可能会漏掉边沿,甚至导致后续一连串错误(因为out结果也是被存起来的)。

如果赋值语句写在else里面,就会有如下错误结果,reset有效期内输入in的0并没有被存储。

最后

以上就是怡然火车最近收集整理的关于HDLBits-Edgecapture的全部内容,更多相关HDLBits-Edgecapture内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复