Verilog刷题HDLBits——Mt2015 q4

- 题目描述

- 代码

- 结果

题目描述

Taken from 2015 midterm question 4

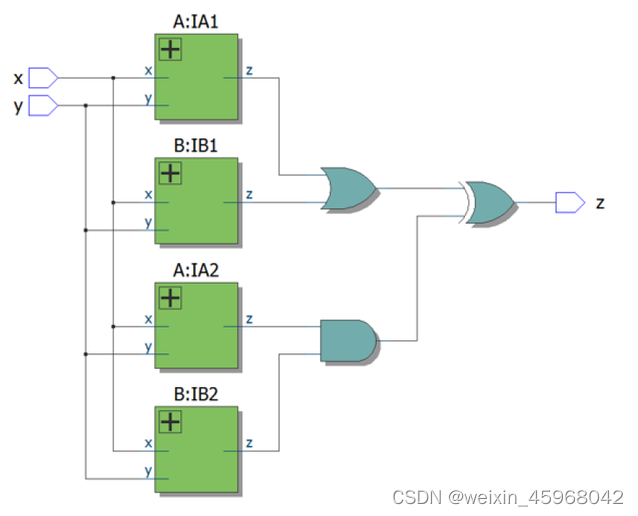

See mt2015_q4a and mt2015_q4b for the submodules used here. The top-level design consists of two instantiations each of subcircuits A and B, as shown below.

代码

// 解法一:不分层

module top_module (input x, input y, output z);

wire z1,z2,z3,z4;

assign z1 = (x^y)&x;

assign z2 = x^~y;

assign z3 = (x^y)&x;

assign z4 = x^~y;

assign z = (z1|z2)^(z3&z4);

endmodule

// 解法二:分层

module top_module(

input x,

input y,

output z);

wire z1, z2, z3, z4;

A ia1 (x, y, z1);

B ib1 (x, y, z2);

A ia2 (x, y, z3);

B ib2 (x, y, z4);

assign z = (z1 | z2) ^ (z3 & z4);

// Or you could simplify the circuit including the sub-modules:

// assign z = x|~y;

endmodule

module A (

input x,

input y,

output z);

assign z = (x^y) & x;

endmodule

module B (

input x,

input y,

output z);

assign z = ~(x^y);

endmodule

结果

最后

以上就是俊秀短靴最近收集整理的关于Verilog刷题HDLBits——Mt2015 q4题目描述代码结果的全部内容,更多相关Verilog刷题HDLBits——Mt2015内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复