For each bit in a 32-bit vector, capture when the input signal changes from 1 in one clock cycle to 0 the next. “Capture” means that the output will remain 1 until the register is reset (synchronous reset).

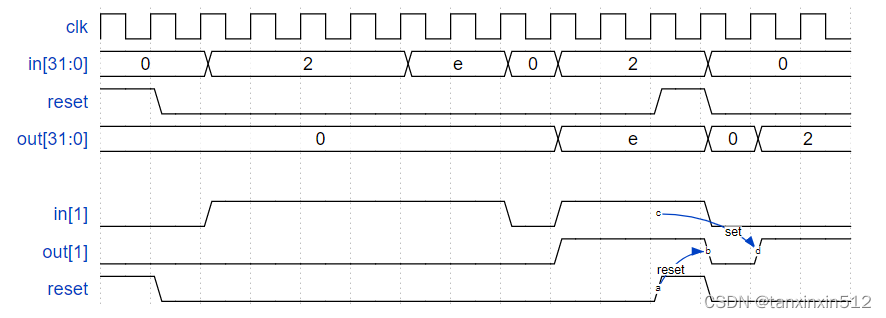

Each output bit behaves like a SR flip-flop: The output bit should be set (to 1) the cycle after a 1 to 0 transition occurs. The output bit should be reset (to 0) at the positive clock edge when reset is high. If both of the above events occur at the same time, reset has precedence. In the last 4 cycles of the example waveform below, the ‘reset’ event occurs one cycle earlier than the ‘set’ event, so there is no conflict here.

In the example waveform below, reset, in[1] and out[1] are shown again separately for clarity.

前言

三个输入,包括一个时钟clk,一个高电平有效的同步置位信号reset,一个输入信号in;一个输出信号out。

代码

module top_module (

input clk,

input reset,

input [31:0] in,

output [31:0] out

);

reg [31:0] in_old;

always@(posedge clk)begin

in_old<=in;

if(reset) out<=32'd0;

else begin

out<=~in&in_old|out;

end

end

endmodule

总结

对于output remain 1的理解,即若是下降沿触发时,out_old为0,则out变为1;若是下降沿未触发,但out_old为1,则out保持,因此out_old和~in&in_old是或的关系。还有就是in_old的赋值问题必须在if循环之前,即时钟一触发就必须赋值,否则会发生赋值延迟错位。

最后

以上就是洁净微笑最近收集整理的关于HDLBits练习——Edgecapture前言代码总结的全部内容,更多相关HDLBits练习——Edgecapture前言代码总结内容请搜索靠谱客的其他文章。

发表评论 取消回复