总结:模块命名注意不能与内置模块同名

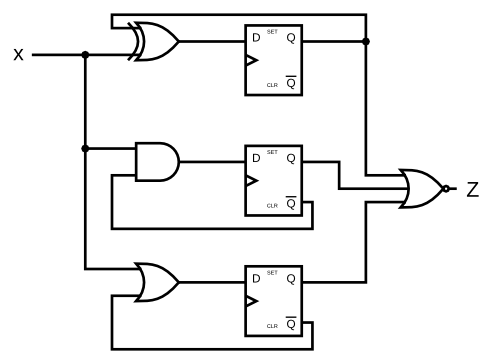

Given the finite state machine circuit as shown, assume that the D flip-flops are initially reset to zero before the machine begins.

Build this circuit.

方法一:模块实例化

1)当按端口名称进行端口对应实例化时,success。

module top_module (

input clk,

input x,

output z

);

/*第一部分的连接*/

wire q0 ;

wire d0 ;

assign d0 = q0 ^ x;

dff dff_module_inst0(.clk(clk),.d(d0),.q(q0));

/*第二部分的连接*/

wire q1 ;

wire d1 ;

assign d1 = ~q1 & x;

dff dff_module_inst1(.clk(clk),.d(d1),.q(q1));

/*第三部分的连接*/

wire q2 ;

wire d2 ;

assign d2 = ~q2 | x;

dff dff_module_inst2(.clk(clk),.d(d2),.q(q2));

/*最后的输出结果*/

assign z = ~(q0 | q1 | q2);

endmodule

/*D触发器模块*/

module dff(input clk,input d,output reg q);

always@(posedge clk) begin

q <= d;

end

endmodule

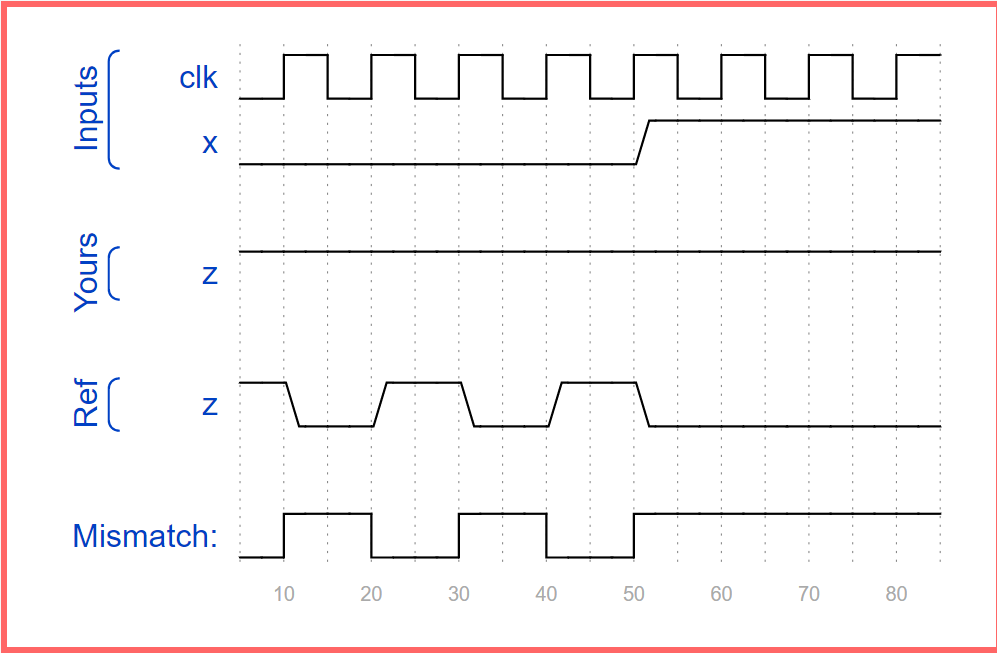

2)当按端口位置实例化时,结果不正确。

代码仅在实例化语句处作更改。

module top_module (

input clk,

input x,

output z

);

/*第一部分的连接*/

wire q0 ;

wire d0 ;

assign d0 = q0 ^ x;

dff dff_module_inst0(clk,d0,q0); //

/*第二部分的连接*/

wire q1 ;

wire d1 ;

assign d1 = ~q1 & x;

dff dff_module_inst1(clk,d1,q1); //

/*第三部分的连接*/

wire q2 ;

wire d2 ;

assign d2 = ~q2 | x;

dff dff_module_inst2(clk,d2,q2); //

/*最后的输出结果*/

assign z = ~(q0 | q1 | q2);

endmodule

/*D触发器模块*/

module dff(input clk,input d,output reg q);

always@(posedge clk) begin

q <= d;

end

endmodule

编译成功,但结果错误。

Status: Incorrect

Compile and simulation succeeded, but the circuit's output wasn't entirely correct. The hints below may help.

# Hint: Output 'z' has 94 mismatches. First mismatch occurred at time 10. # Hint: Total mismatched samples is 94 out of 115 samples

原因查明为d触发器模块名称为内置模块名称,所引起冲突,造成错误。

Warning (12018): Entity "dff" will be ignored because it conflicts with Quartus Prime primitive name File: /home/h/work/hdlbits.3688841/top_module.v Line: 28

Quartus has a number of built-in "primitive" modules. Don't give any of your modules the same name as a primitive. This message warns you that you are instantiating the built-in primitive instead of your module.

将dff修改为mydff后,success

module top_module (

input clk,

input x,

output z

);

/*第一部分的连接*/

wire q0 ;

wire d0 ;

assign d0 = q0 ^ x;

mydff dff_module_inst0(clk,d0,q0);

/*第二部分的连接*/

wire q1 ;

wire d1 ;

assign d1 = ~q1 & x;

mydff dff_module_inst1(clk,d1,q1);

/*第三部分的连接*/

wire q2 ;

wire d2 ;

assign d2 = ~q2 | x;

mydff dff_module_inst2(clk,d2,q2);

/*最后的输出结果*/

assign z = ~(q0 | q1 | q2);

endmodule

/*D触发器模块*/

module mydff(input clk,input d,output reg q);

always@(posedge clk) begin

q <= d;

end

endmodule

再改变一下排版,依旧success

module top_module (

input clk,

input x,

output z

);

wire d0,d1,d2;

wire q0,q1,q2;

assign d0 = q0 ^ x;

assign d1 = ~q1 & x;

assign d2 = ~q2 | x;

mydff mydff_inst0(clk,d0,q0);

mydff mydff_inst1(clk,d1,q1);

mydff mydff_inst2(clk,d2,q2);

assign z = ~(q0 | q1 | q2);

endmodule

module mydff (input clk,input d,output reg q);

always @(posedge clk) begin

q <= d;

end

endmodule

方法二:

module top_module (

input clk,

input x,

output z

);

wire q0,q1,q2;

always @(posedge clk) begin

q0 <= x ^ q0;

q1 <= x & ~q1;

q2 <= x | ~q2;

end

assign z = ~(q0 | q1 | q2);

endmodule

最后

以上就是唠叨丝袜最近收集整理的关于Exams/ece241 2014 q4经验的全部内容,更多相关Exams/ece241内容请搜索靠谱客的其他文章。

发表评论 取消回复