Taken from 2015 midterm question 4

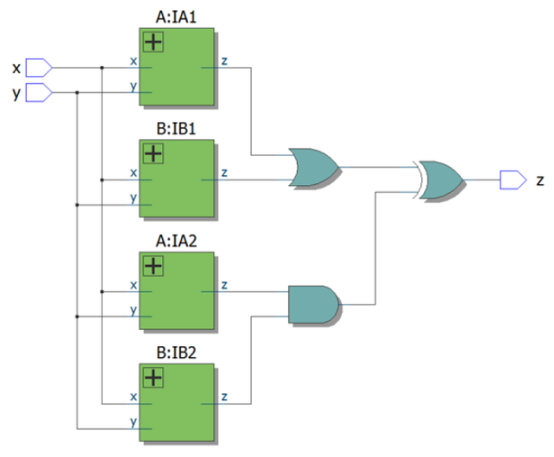

See mt2015_q4a and mt2015_q4b for the submodules used here. The top-level design consists of two instantiations each of subcircuits A and B, as shown below.

Implement this circuit.

第一种是使用module

module top_module (input x, input y, output z);

wire z1,z2,z3,z4;

a a_instance1(

.x(x),

.y(y),

.z(z1)

);

a a_instance2(

.x(x),

.y(y),

.z(z3)

);

b b_instance1(

.x(x),

.y(y),

.z(z2)

);

b b_instance2(

.x(x),

.y(y),

.z(z4)

);

assign z = (z1|z2)^(z3&z4);

endmodule

module a (

input wire x,

input wire y,

output wire z

);

assign z = (x^y) & x;

endmodule

module b (

input wire x,

input wire y,

output wire z

);

assign z = ~x^y;

endmodule

第二种是使用task,从下面代码中可以看出来,同一个module的不同task的参数名是可以一样的,不会冲突,我理解可以认为就是局部变量;另外需要注意的就是task的调用必须在过程块中,比如always。

module top_module (input x, input y, output z);

wire wire1,wire2,wire3,wire4;

always@(*)begin

A(x,y,wire1);

A(x,y,wire2);

B(x,y,wire3);

B(x,y,wire4);

end

assign z = (wire1|wire2)^(wire3&wire4);

//--------------task A-------------------

task A;

input x,y;

output z;

z = (x ^ y) & x;

endtask

//------------------task B-----------------

task B;

input x,y;

output z;

z = (x == y)?1:0;

endtask

endmodule最后

以上就是优秀芒果最近收集整理的关于【HDLBits刷题】Mt2015 q4.的全部内容,更多相关【HDLBits刷题】Mt2015内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复