获取原理:

不管是取下降沿还是上升沿,都得设置标志位,即指示信号,在信号下降沿来的时候指示信号要拉高。

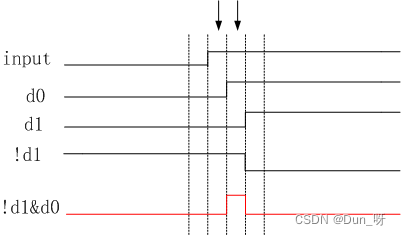

在获取上升沿的时,此时的信号从0→1,而上一时刻的旧信号还是0,此时应该把旧信号取反与当前信号与操作,即(当前信号)&&(~旧信号)。

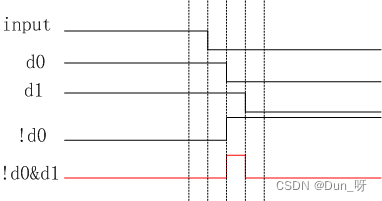

在获取下降沿时,此时信号从1→0,而上一时刻的旧信号还是1,此时应该把当前信号进行取反与上一时刻的旧信号与操作,即(~当前信号)&&(旧信号)。

下面两幅图可以做参考:

上图为了防止亚稳态,把输入信号input进行打两拍操作,下降沿将第一拍取反,与第二拍相与操作,下降沿指示信号得到高电平,上升沿将第二拍信号取反,与第一拍信号相与操作,上升沿指示信号得到高电平。

最后

以上就是激情镜子最近收集整理的关于Verilog取信号的上升沿与下降沿的全部内容,更多相关Verilog取信号内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复