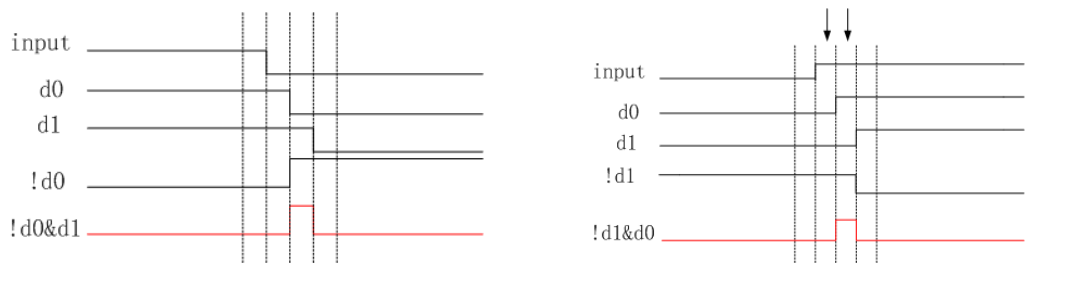

如图所示,当检测下降沿时,初始化两个寄存器为高电平;当检测上升沿时,初始化两个寄存器位低电平。当输入信号变化时候,只能在下一个时钟周期检测得到。

下降沿检测:

1.输入信号打两拍 2.第一拍的信号取反和第二拍进行与运算

reg uart_rxd_d0;

reg uart_rxd_d1;

//wire define

wire start_flag;

assign start_flag = uart_rxd_d1 & (~uart_rxd_d0);

//对发送信号延迟两个时钟周期

always @(posedge sys_clk or negedge sys_rst_n) begin

if (!sys_rst_n) begin

uart_rxd_d0 <= 1'b1;

uart_rxd_d1 <= 1'b1;

end

else begin

uart_rxd_d0 <= uart_rxd; //uart_rxd为输入数据,检测它的下降沿

uart_rxd_d1 <= uart_rxd_d0;

end

end

上升沿检测:

1.输入信号打两拍 2.将第二拍的信号取反与第一拍进行与运算

reg uart_en_d0;

reg uart_en_d1;

//wire define

wire en_flag;

assign en_flag = (~uart_en_d1) & uart_en_d0;

//对发送信号延迟两个时钟周期

always @(posedge sys_clk or negedge sys_rst_n) begin

if (!sys_rst_n) begin

uart_en_d0 <= 1'b0;

uart_en_d1 <= 1'b0;

end

else begin

uart_en_d0 <= uart_en; //输入信号,需要检测其上升沿

uart_en_d1 <= uart_en_d0;

end

end

最后

以上就是纯真大地最近收集整理的关于输入信号上升沿或者下降沿检测 Verilog代码的全部内容,更多相关输入信号上升沿或者下降沿检测内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复