文章目录

- 题目

- 题解

-

- 三段式(不通过,只是延迟了一拍)

- 两段式(通过)

题目

描述

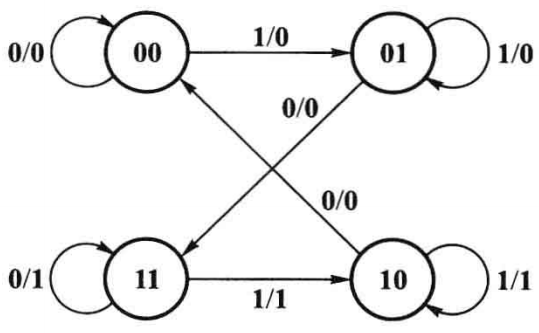

某同步时序电路的状态转换图如下,→上表示“C/Y”,圆圈内为现态,→指向次态。

请使用D触发器和必要的逻辑门实现此同步时序电路,用Verilog语言描述。

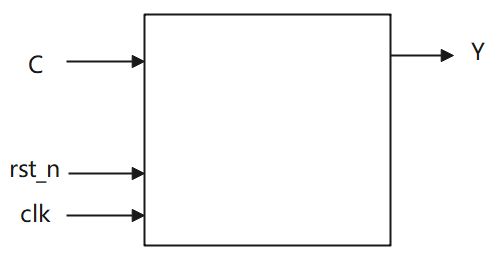

电路的接口如下图所示,C是单bit数据输入端。

输入描述:

最后

以上就是风趣台灯最近收集整理的关于【校招Verilog快速入门】时序逻辑篇:VL22、根据状态转移图实现时序电路(FSM)题目的全部内容,更多相关【校招Verilog快速入门】时序逻辑篇内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复