文章目录

- 前言

- 一、题目描述:

- 二、实现思路

- 1.先了解T触发器的相关知识

- 2.区分异步复位和同步复位

- 1)异步复位

- 2)同步复位

- 3)同步复位和异步复位的优缺点

- 3.从波形中得到的信息

- 三、代码展示

- 总结

前言

今天我们做的是第二道题——异步复位的串联T触发器,可能有些人听名字就觉得这道题比较难,但其实它并没有想象中的那么难,它仅仅只是两个T触发器串联而已,接下来我们便去看看如何写这道题。异步复位的串联T触发器

一、题目描述:

用 Verilog 实现两个串联的异步复位的T触发器的逻辑。

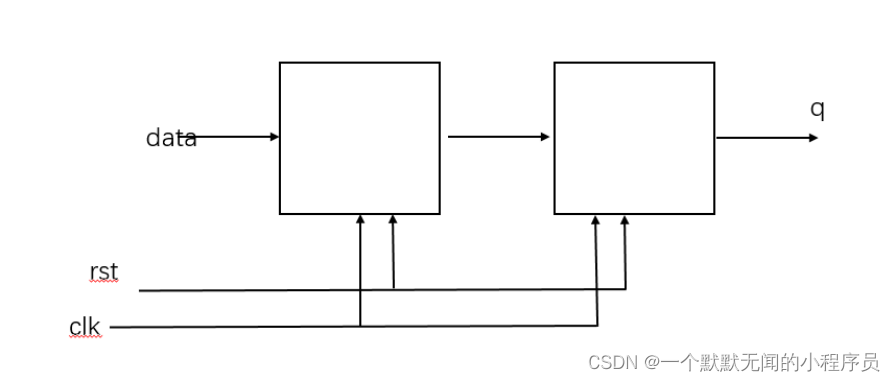

信号示意图:

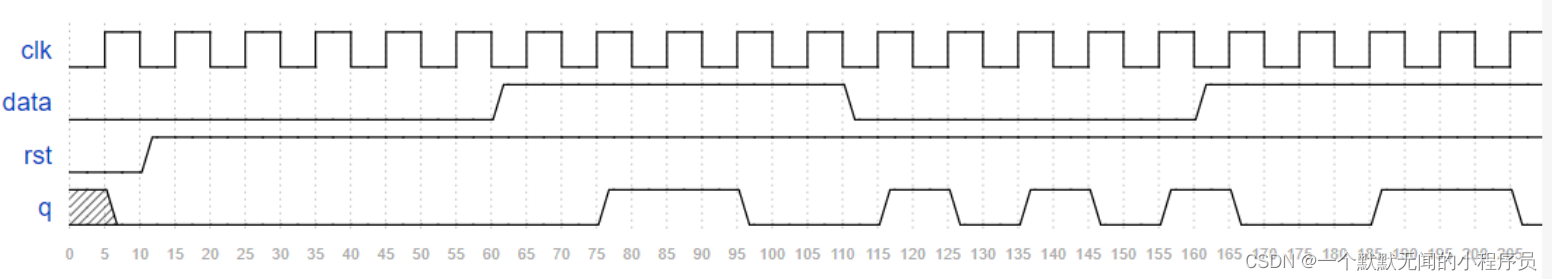

波形示意图:

输入描述:

输入信号 data, clk, rst

类型 wire

在testbench中,clk为周期5ns的时钟,rst为低电平复位

输出描述:

输出信号 q

类型 reg

二、实现思路

1.先了解T触发器的相关知识

1)构成:将JK触发器的输入端J、K连接在一起,作为输入端T,就构成了T触发器。

2)特性方程:

Qn+1 = T Qn ’ +T ’ Qn= T⊕Qn (其中Qn为现态,Qn+1为次态)

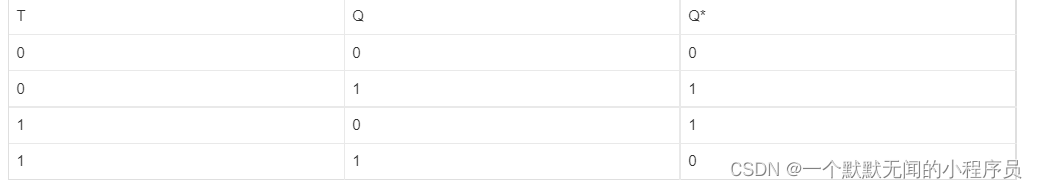

3)特性表

4)功能

当输入T为0时,Qn+1=Qn(保持);当输入T为1时,Qn+1=~Qn(翻转)。

5)实现代码

if(data_in == 1’b1)

data_out <= ~data_out;

else

data_out <= data_out;

2.区分异步复位和同步复位

1)异步复位

异步复位就是复位是异步的,与时钟触发边沿无关。复位信号一旦来临就使得寄存器进行复位操作,_复位信号出现在always块的敏感列表里。

对于异步的低电平复位,是以下降沿作为触发边沿(高电平变为低电平的时刻),并且触发后判断复位是否为低电平,用代码表示为:

always @ (posedge clk or negedge rst)

begin

if( ~rst )

...;

else

...;

end

异步高电平复位用代码表示为:

always @ (posedge clk or posedge rst)

begin

if( rst )

...;

else

...;

end

2)同步复位

同步复位时,复位与时钟触发沿有关,所以在always的敏感变量中,只有时钟触发边沿,然后根据高电平或者低电平再判断复位电平。

同步低电平复位用代码表示为:

always @ (posedge clk)

begin

if( ~rst )

...;

else

...;

end

同步高电平复位用代码表示为:

always @ (posedge clk)

begin

if( rst )

...;

else

...;

end

3)同步复位和异步复位的优缺点

异步复位:反应快,复位电平可以小于一个时钟周期,有些触发器只有异步复位端口;

同步复位:稳定,不易受毛刺干扰,有些模块只有同步复位端口;

3.从波形中得到的信息

由 ret 和 q 的波形看出该触发器是异步低电平复位,在 rst 为高电平时数据有效

三、代码展示

`timescale 1ns/1ns

module Tff_2 (

input wire data, clk, rst,

output reg q

);

reg q1;

always @ (posedge clk or negedge rst)

begin

if(!rst) begin

q1 <= 1'b0;

end

else begin

if( data == 1'b1)

q1 <= ~q1;

else

q1 <= q1;

end

end

always @ (posedge clk or negedge rst)

begin

if(!rst) begin

q <= 1'b0;

end

else begin

if( q1 == 1'b1)

q <= ~q;

else

q <= q;

end

end

endmodule

总结

这是我对异步复位的串联T触发器的理解以及代码的编写,如果还有更多更好的解法,欢迎读到这篇文章的朋友们在评论区告诉我,共同进步嘛。

最后

以上就是彪壮棒棒糖最近收集整理的关于Verilog学习之异步复位的串联T触发器设计前言一、题目描述:二、实现思路三、代码展示总结的全部内容,更多相关Verilog学习之异步复位内容请搜索靠谱客的其他文章。

发表评论 取消回复