异步复位的串联T触发器

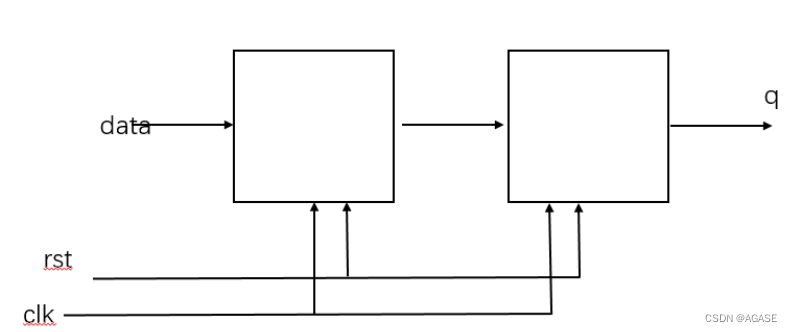

题目描述:用verilog实现两个串联的异步复位的T触发器的逻辑,结构如图:

编写代码思路:

T触发器的特性是T=0时,输出状态与前一级输出状态相同,即输出状态保持不变;T=1时,输出状态与前一级输出状态相反,即输出状态翻转。

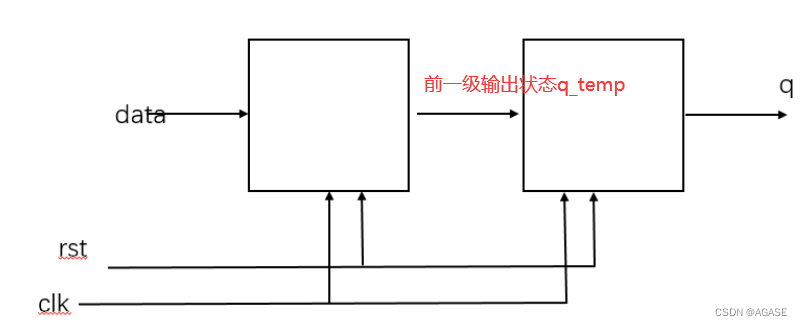

设置一个temp状态q_temp表示前一级输出状态,如下图所示

`timescale 1ns/1ns

module Tff_2 (

input wire data, clk, rst,

output reg q

);

//*************code***********//

reg q_temp;

always @(posedge clk or negedge rst)begin

if(!rst)

q_temp <= 1'b0;

else if(data)

q_temp <= ~q_temp;

else

q_temp <= q_temp;

end

always @(posedge clk or negedge rst)begin

if(!rst)

q <= 1'b0;

else if(q_temp)

q <= ~q;

else

q <= q;

end

//*************code***********//

endmodule

最后

以上就是正直毛豆最近收集整理的关于牛客Verilog刷题:异步复位的串联T触发器的全部内容,更多相关牛客Verilog刷题:异步复位内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复