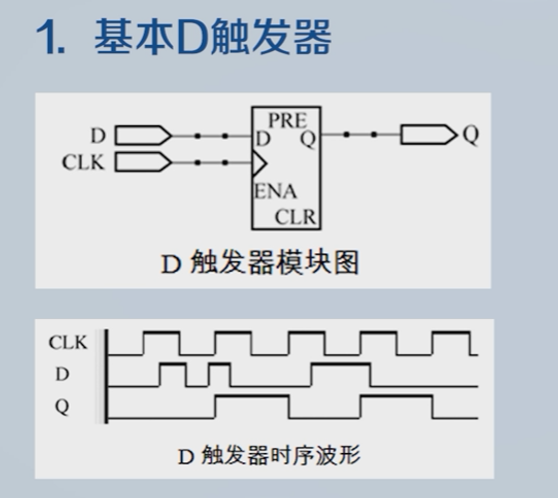

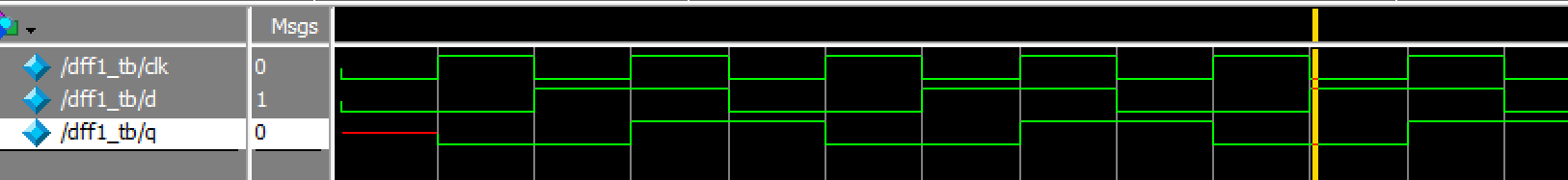

只有时钟clk:

Q由D控制,Q=D,但在clk时钟上升沿才会改变

// 2022-1-27 verilog 学习

// D触发器

`timescale 1ns/10ps

module dff1(clk, d, q);

input clk,d;

output q;

reg q; // 由always敏感变量控制的量是reg

always @(posedge clk) // 只在时钟上升沿改变

begin

q <= d;

end

endmodule

// ------testbench----

module dff1_tb;

reg clk,d;

wire q;

dff1 dff1(

.clk(clk),

.d(d),

.q(q)

);

initial begin

d<=0;clk<=0; //reg初值

#100 $stop;

end

always #5 clk = ~clk;

always #10 d <= d+1;

endmodule

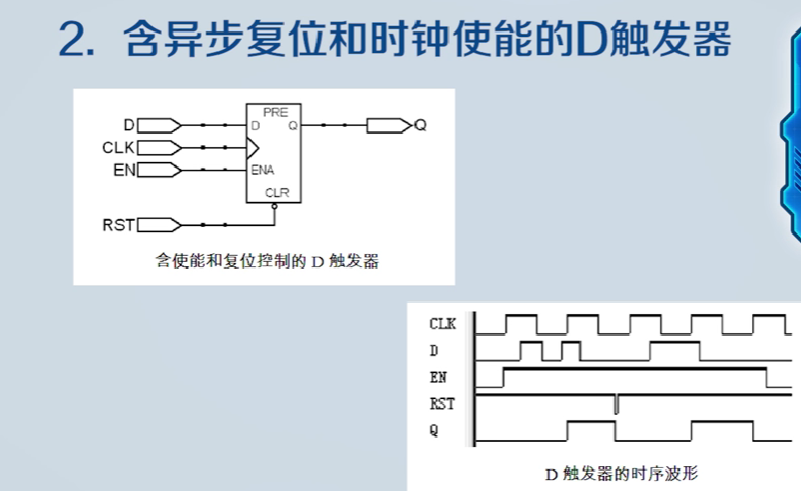

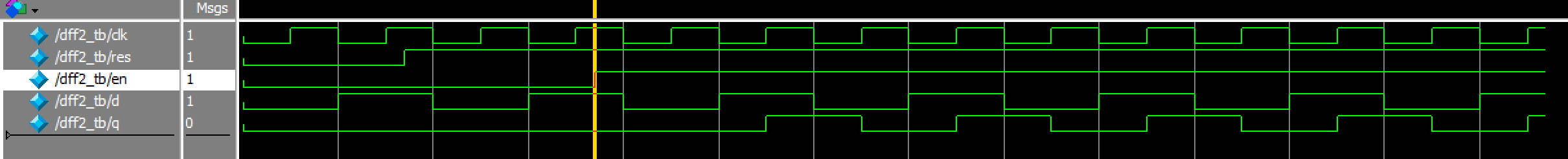

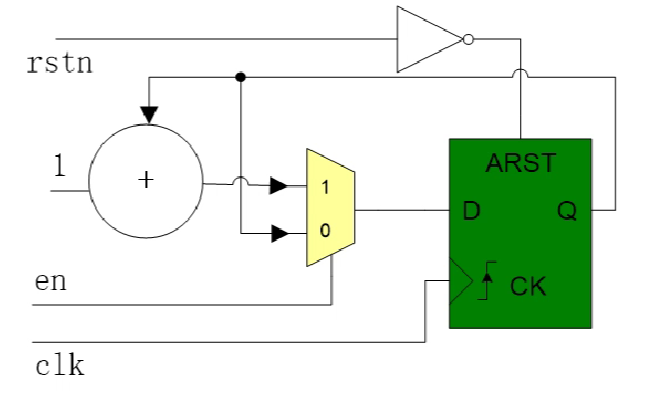

时钟clk,使能en,复位res:

// 2022-1-27 verilog 学习

// D触发器 clk res en

`timescale 1ns/10ps

module dff2(clk, res, en, d, q);

input clk;

input res;

input en;

input d;

output q;

reg q;

always@(posedge clk or negedge res)

begin

if(~res)

begin

q<=0;

end

else begin

if(en)

begin

q <= d;

end

end

end

endmodule

// ------testbench----

module dff2_tb;

reg clk,res,en,d;

wire q;

dff2 dff2(

.clk(clk),

.res(res),

.en(en),

.d(d),

.q(q)

);

initial begin

d<=0;clk<=0;res<=0;en<=0; //reg初值

#17 res<=1;

#20 en<=1;

#100 $stop;

end

always #5 clk = ~clk;

always #10 d <= d+1;

endmodule

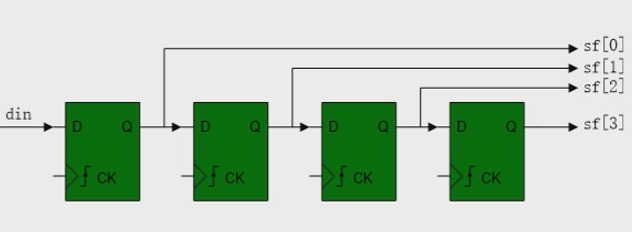

移位寄存器

图中箭头所示,数据移动方向为从左到右,观察各个D触发器输出连接的名称,即 s[2] 移给 s[3],往高位移动,左移

// 左移 写法一

sf[3:1] = sf[2:0]; // 原来的sf[2:0]赋值给现在的sf[3:1]

sf[0] = din; // 现在的sf[0]用din补上

// 左移 写法二

sf = sf{sf[2:0], din}

// 右移 写法一

sf[2:0] = sf[3:1];

sf[3] = din;

// 右移 写法二

sf = sf{din, sf[3:1] }

计数器

cnt = cnt+1;

最后

以上就是怡然蜜蜂最近收集整理的关于verilog D触发器只有时钟clk:时钟clk,使能en,复位res:的全部内容,更多相关verilog内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复