个人笔记。

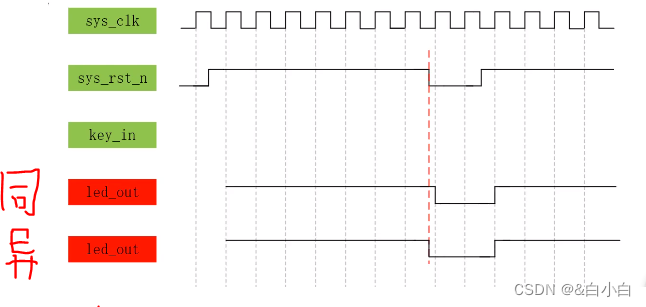

同步复位输出信号led_out不会因为复位信号sys_rst_n拉低了就立刻拉低,只有在时钟信号sys_clk上升沿检测到复位信号拉低了才会拉低,复位信号拉高时只有在时钟信号上升沿输出信号才会拉高。

异步复位输出信号led_out,只要复位信号拉低了就立刻拉低,不考虑时钟沿,复位信号拉高时只有在时钟信号上升沿输出信号才会拉高。

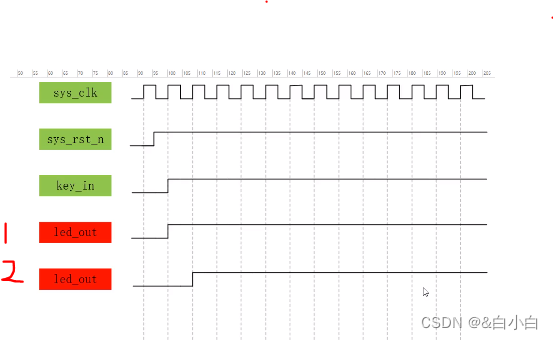

1为组合逻辑输出信号,2为时序逻辑输出信号

组合逻辑时,时钟上升沿采集到的输入信号key_in的高电平,那么输出信号就是高电平。高时序逻辑时,时钟上升沿与输入信号对齐,默认当前时钟沿采集到的数据是在该时钟上升沿前一时刻的值,如图时钟上升沿前一时刻key_in为低电平,所以2为低电平 ,前一时刻key_in为高电平,所以2为高电平。(延迟一拍)

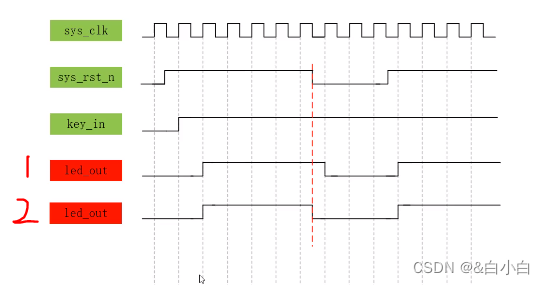

1为时序逻辑同步复位输出信号,2为时序逻辑异步复位输出信号

最后

以上就是害怕万宝路最近收集整理的关于【学习笔记-FPGA】寄存器的同步复位与异步复位、组合逻辑与时序逻辑的全部内容,更多相关【学习笔记-FPGA】寄存器内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复