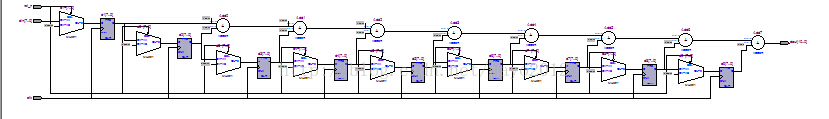

放寒假之前有打算用FPGA实现JPEG的编解码的,都知道二维DCT变换又是JPEG编解码的核心,于是就试着先用FPGA实现DCT变换。熟悉DCT变换公式的可能都知道图像的DCT变换,实际上就是用一组DCT系数与模板覆盖下的对应像素强度的乘累加。所以我们可以事先将DCT变换系数存在FPGA的ROM里,在做的过程中发现了一个问题那就是建立时间(setup time)得不到满足。经过检查发现,问题就出在DCT变换过程中的加法上,我在求最后的DCT变换结果时,直接将乘的结果送到加法器中,类似于这样的形式:

assign q_sum = q0+(q1<<1)+(q2<<2)+(q3<<3)+(q4<<4)+(q5<<5)+(q6<<6)+(q7<<7)+(q8<<8)+(q9<<9);

大神看到之后估计会笑喷了,如此长的加法链,如此长的组合逻辑,真实想不满足建立时间都难啊。

于是当时就把这个加法改了下:q0与(q1<<1)相加后,结果通过寄存器缓存一拍。类似的q3与q4,q5与q6,q7与q8,好吧q9落单了,但也只能乖乖的自己打入寄存器缓存一拍。

改过之后,发现建立时间得到改善,但余量仍是负的,只能在乖乖的在往后插入寄存器了。最终建立时间得到了满足,可以跑50M了,

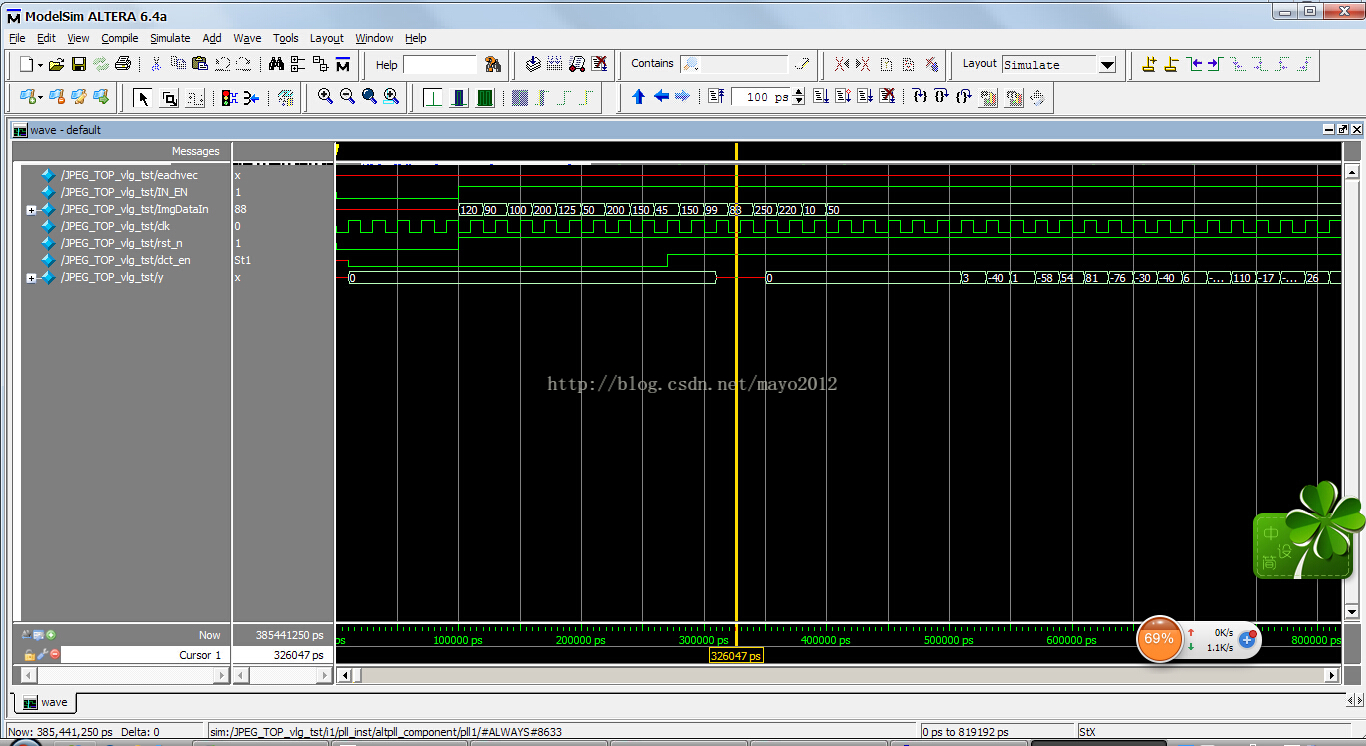

下面是仿真的结果

k

k

可以看到输出迟滞还是有点大的是,原因就是加法链中插入了过多的寄存器。

通过这些例子也告诫自己,在以后的FPGA设计中,对于组合逻辑的设计一定要小心,可以通过插入寄存器的方式分割较长的组合逻辑以达到时序优化的目的。

最后

以上就是舒心发箍最近收集整理的关于时序优化之使用寄存器分割较长的组合逻辑的全部内容,更多相关时序优化之使用寄存器分割较长内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复