学完后的收获:什么是寄存器,它能做什么、有什么特性、如何用 Verilog 语言来描述。

组合逻辑最大的缺点就是会存在竞争冒险,时序逻辑最基本的单元就是寄存器,寄存器具有存储功能,一般是由 D 触发器构成,由时钟脉冲控制,每个 D 触发器(D Flip Flop ,DFF)能够存储一位二进制码。

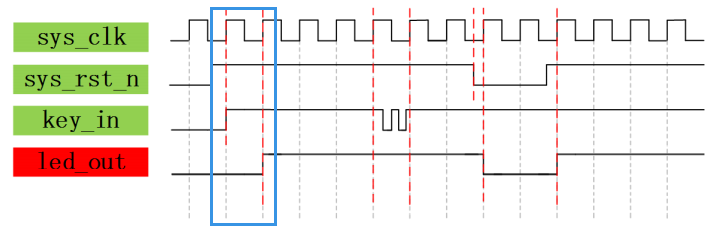

其复位又分为同步复位和异步复位。同步复位的 D 触发器中的“同步”是和工作时钟同步的意思,异步复位的 D 触发器中的“异步”是和工作时钟不同步的意思。主要就是复位有效的条件是“立刻”执行还是等待“沿”再执行的区别。

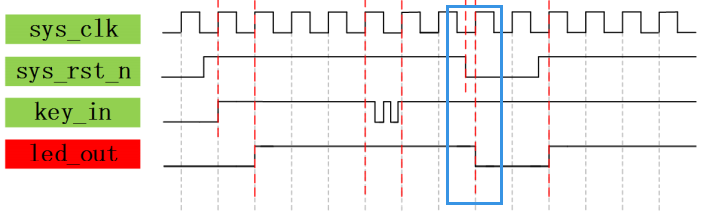

同步复位:sys_rst_n 被拉低后 led_out 没有立刻变为 0,而是当 syc_clk 的上升沿到来的时候 led_out 才复位成功

时序电路还有一个特点,就是“延一拍”的效果。

当表达时序逻辑时如果时钟和数据是对齐的,则默认当前时钟沿采集到的数据为在该时钟上升沿前一时刻的值;当表达组合逻辑时如果时钟和数据是对齐的,则默认当前时钟沿采集到的数据为在该时钟上升沿同一时刻的值。

我们在画波形图的时候一定要记住这个“延一拍”的效果,否则我们绘制的波形图就会和最后的仿真结果不符,也可能会导致最后的逻辑混乱。

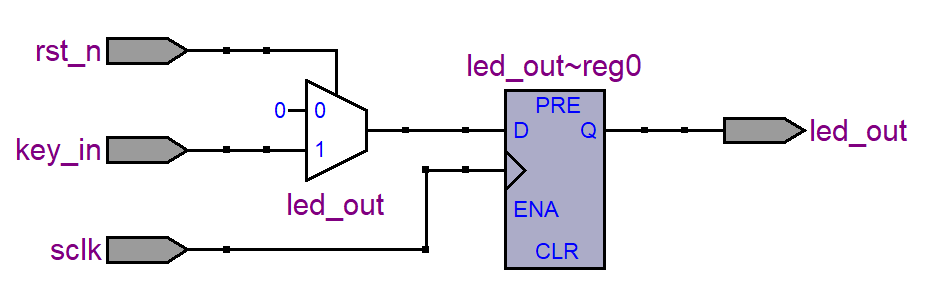

同步复位的D触发器的HDL描述

module flip_flop

(

input wire sclk ,

input wire rst_n ,

input wire key_in ,

output reg led_out

);

always@(posedge sclk) begin//同步复位:当敏感列表为检测到sclk上升沿时执行下面的语句

if(rst_n == 1'b0)//大前提是:sclk的上升沿到来时

led_out <= 1'b0;

else

led_out <= key_in;

end

endmodule

综合出的RTL图为

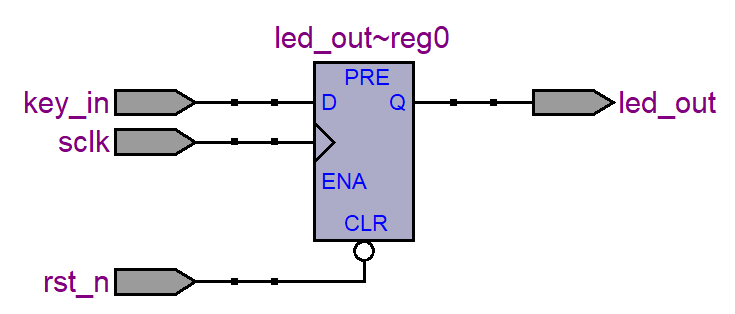

异步复位的D触发器的HDL描述

module flip_flop_1

(

input wire sclk ,

input wire rst_n ,

input wire key_in ,

output reg led_out

);

always@(posedge sclk or negedge rst_n)//异步复位

if(rst_n == 1'b0)//检测到rst_n的下降沿时立即复位,不需要等待sclk的上升沿来到后载复位

led_out <= 1'b0;

else

led_out <= key_in;

endmodule

最后

以上就是紧张紫菜最近收集整理的关于【实验】寄存器的全部内容,更多相关【实验】寄存器内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复