引言

相信很多学习Verilog的同学都是以C语言作为第一计算机母语开始学习,在学习Verilog中我们特别经常会使用大量的逻辑运算符,例如 :与(&)、或(|)、非(~)、异或(^)等等逻辑运算符,同时还有+,-,*,/,%等算术运算符,而大家也经常弄不明白例如:

标准形式: ~(in1|in2)是否可以被描述为: in1|~in2 、或者是in1 ~|in2、又或者是 ~in1|in2 等等的细节问题。今天我们就来梳理一下,Verilog中的逻辑运算符。

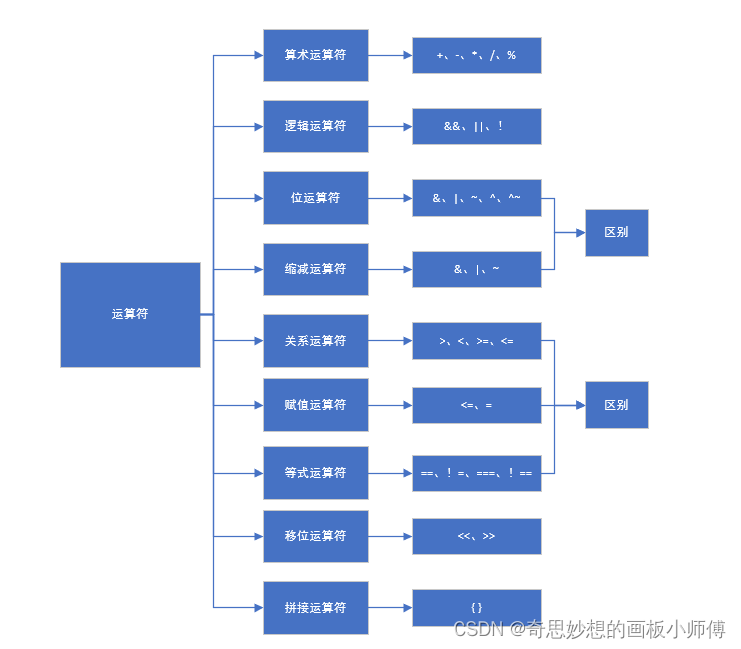

分类

图片是我梳理的Verilog常接触的几类运算符,平时使用的还有一个三目运算符比较特殊没有列上,今天我们重点来区分记忆一下逻辑运算类的运算符:

正文

- 第一重要的逻辑类运算符: 位运算符 与 逻辑运算符

- 其次: 缩位运算符与 等式运算符

逻辑运算符:&&、||、!

&&和||是双目运算符,用在两数之间: A && B 或者 A || B ;&&A 、|| A为非法。

! 是单目运算符,一般用在数字之前 : !A ; A!为非法。

想要真正理解逻辑运算符的关键,在于理解逻辑运算符比较的量不在于值本身,而在于这个值的“真”与“假”

这是什么意思呢? 逻辑运算的一个核心就是“ Z = A xx B ”,这里的A、B、Z都只有两个值:True or Fals ;而 true 和 false 在机器中常表示为 1 和 0;

所以 ,如果一个四位二进制数A,当A为 0010或者0001等等值时则 A代表 true ,只有当A为 0000时才为false。

不大相信?咱们实践出真知!

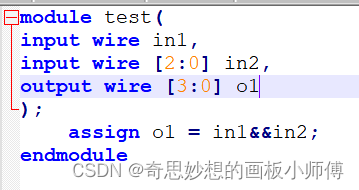

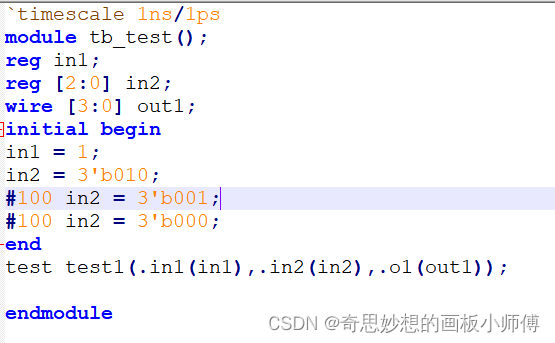

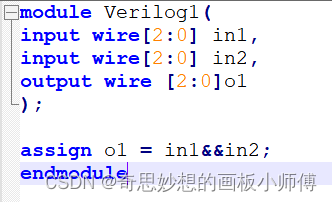

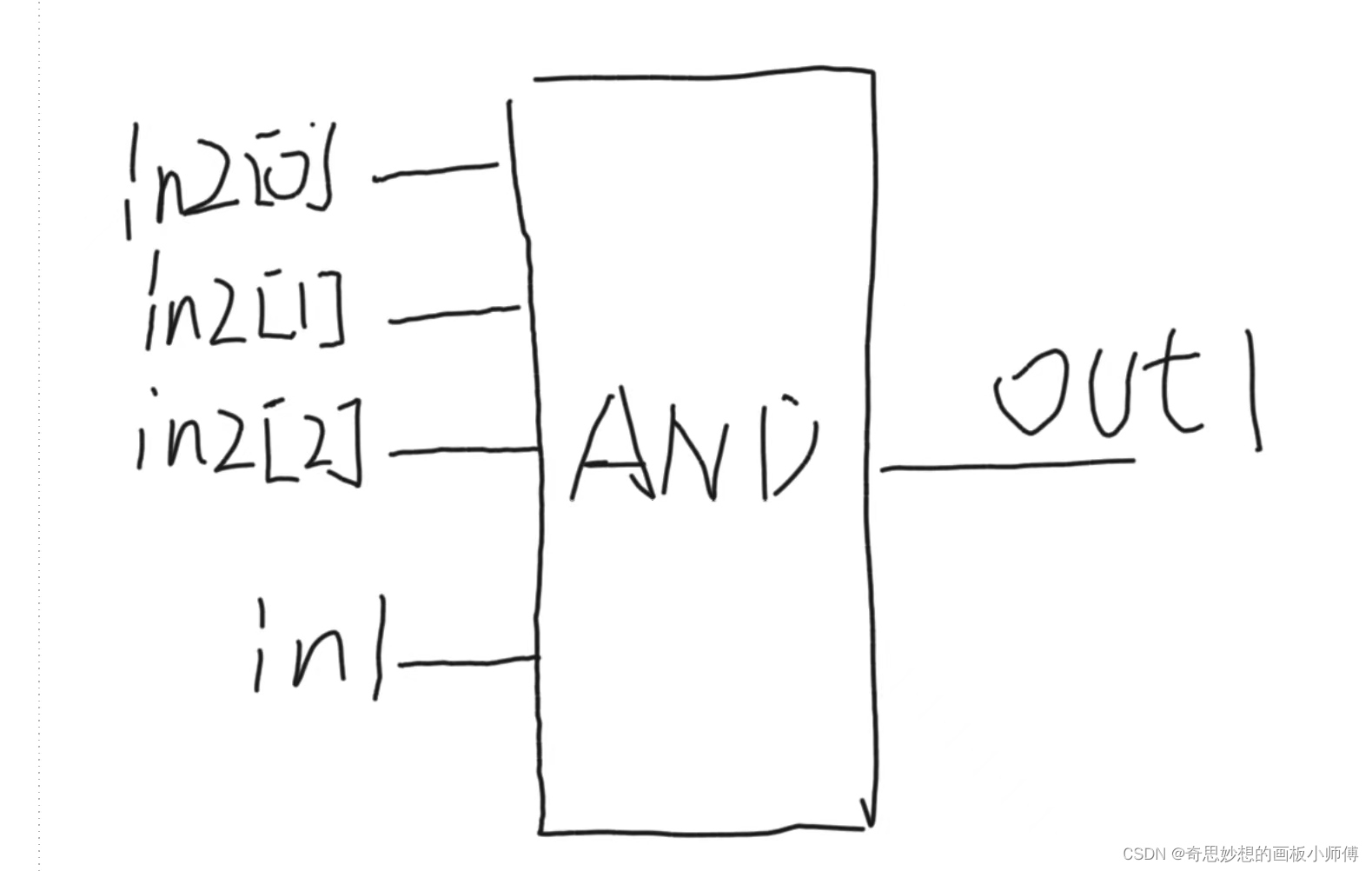

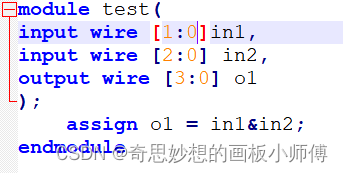

test的功能是将 in1与 in2进行逻辑与,看好哦,in1与in2宽度不相等!

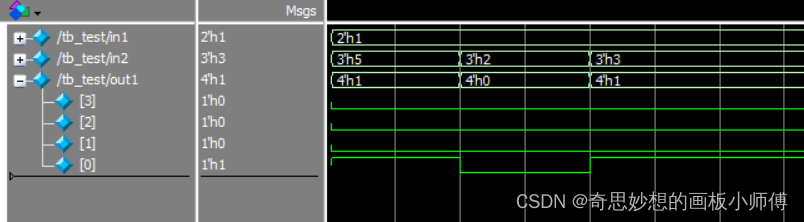

仿真文件意思是初始值 in1为1,in2由 010 变为001 变为000

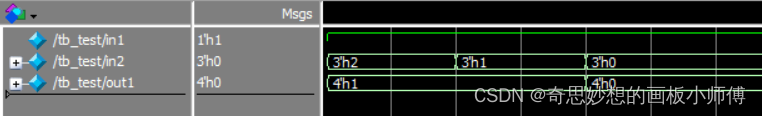

结果说明 ,当in1为010和001时输出的结果都是一样的,也就是说 010和001其实都代表着真,只有当in1 = 000时代表假,所以输出变成0

所以:有同学疑问:逻辑运算符是否可以运算不同位宽的两个数呢?

结论:参与逻辑运算的两个变量位宽不需要一致

还有同学疑惑:逻辑运算的结果是几位的呢?

查看波形图可知:四位的out1只有第0位置 “1”其余位都为“0”

结论:逻辑运算的结果为 “0” 或者“1”(即“真”or“假”)

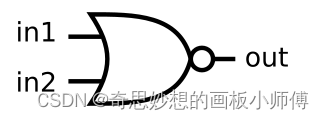

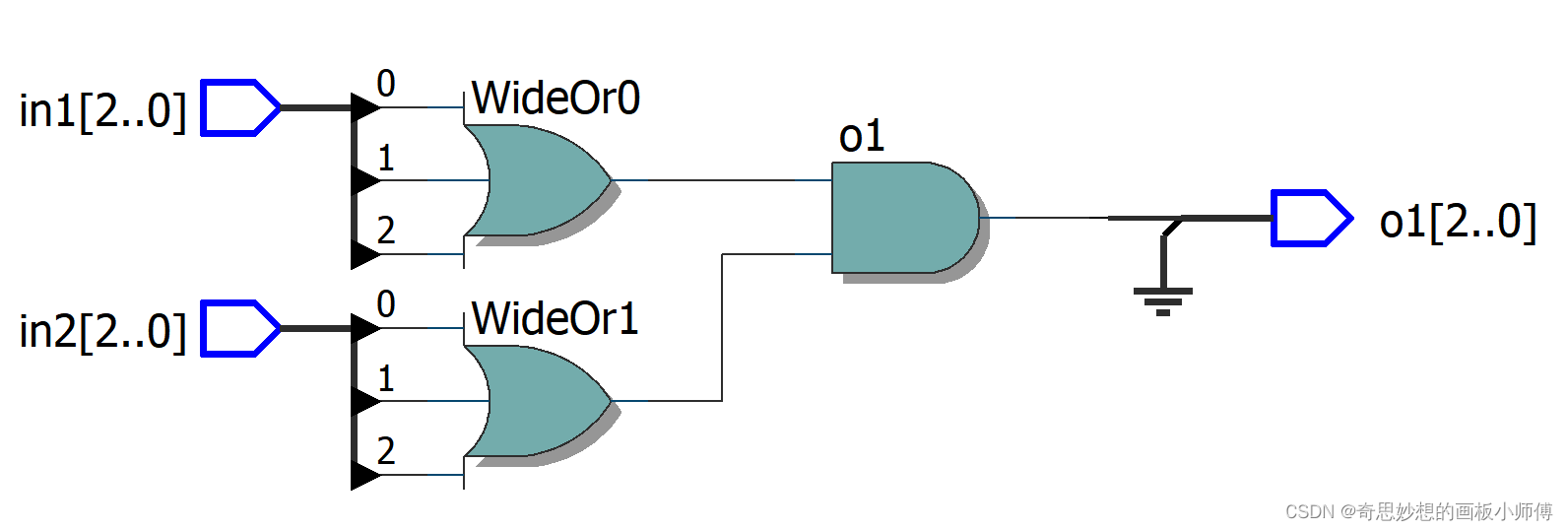

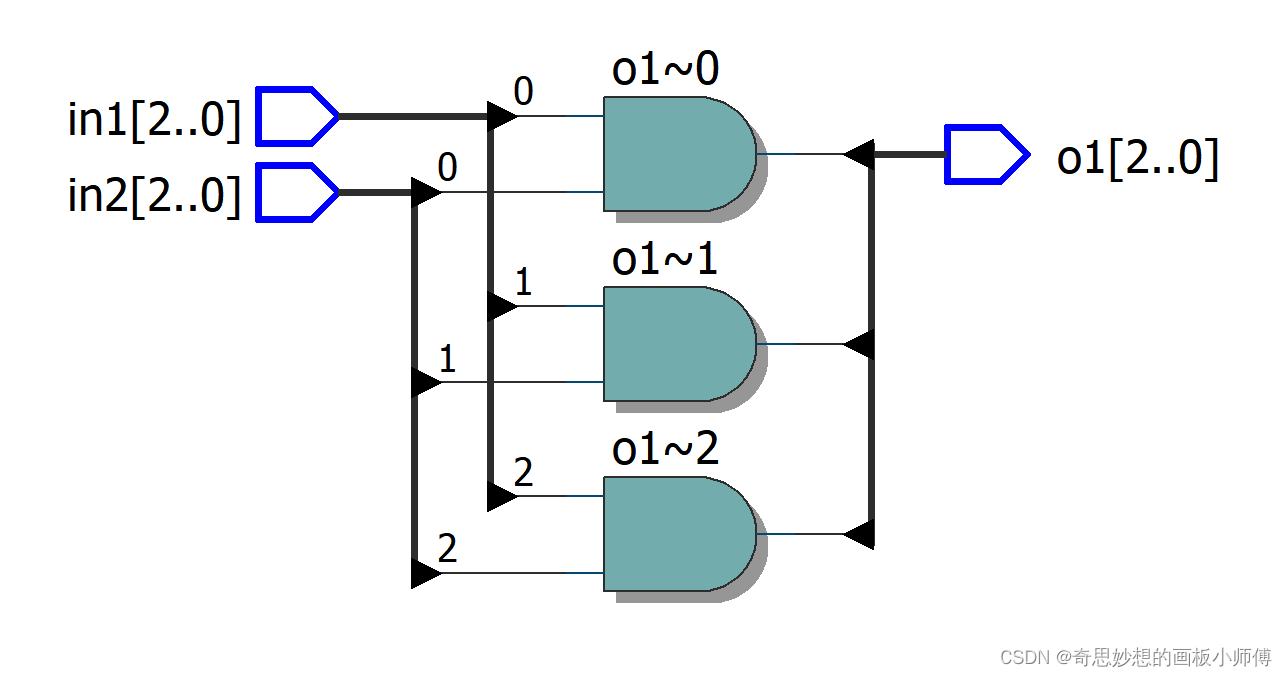

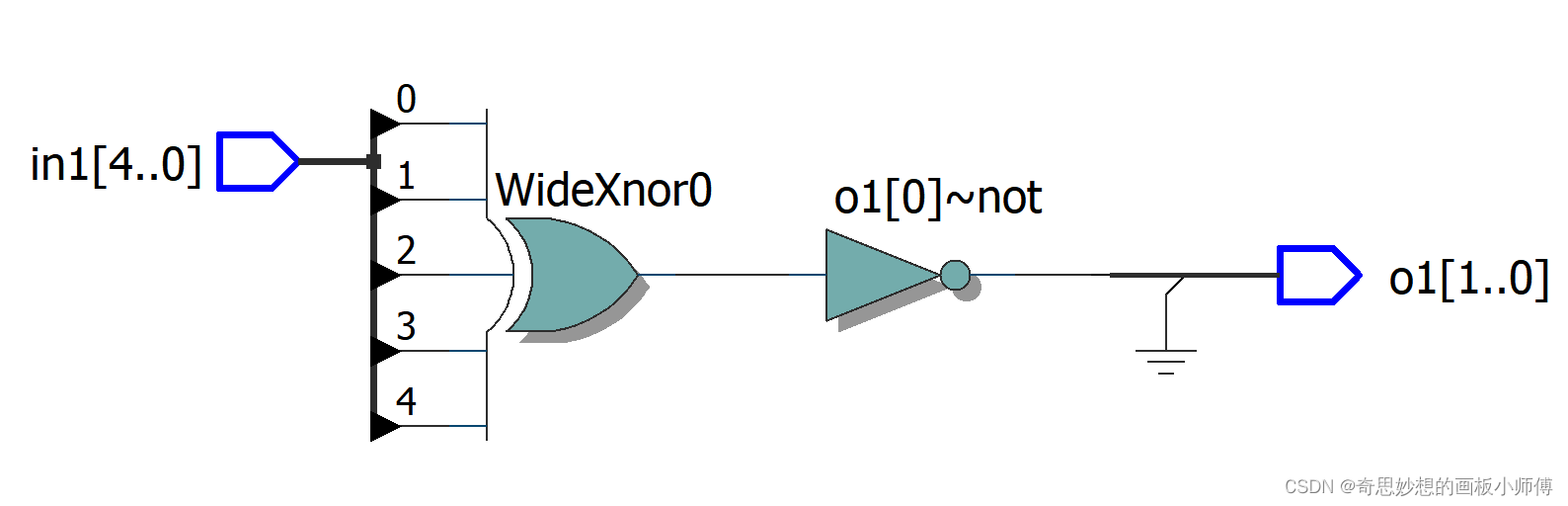

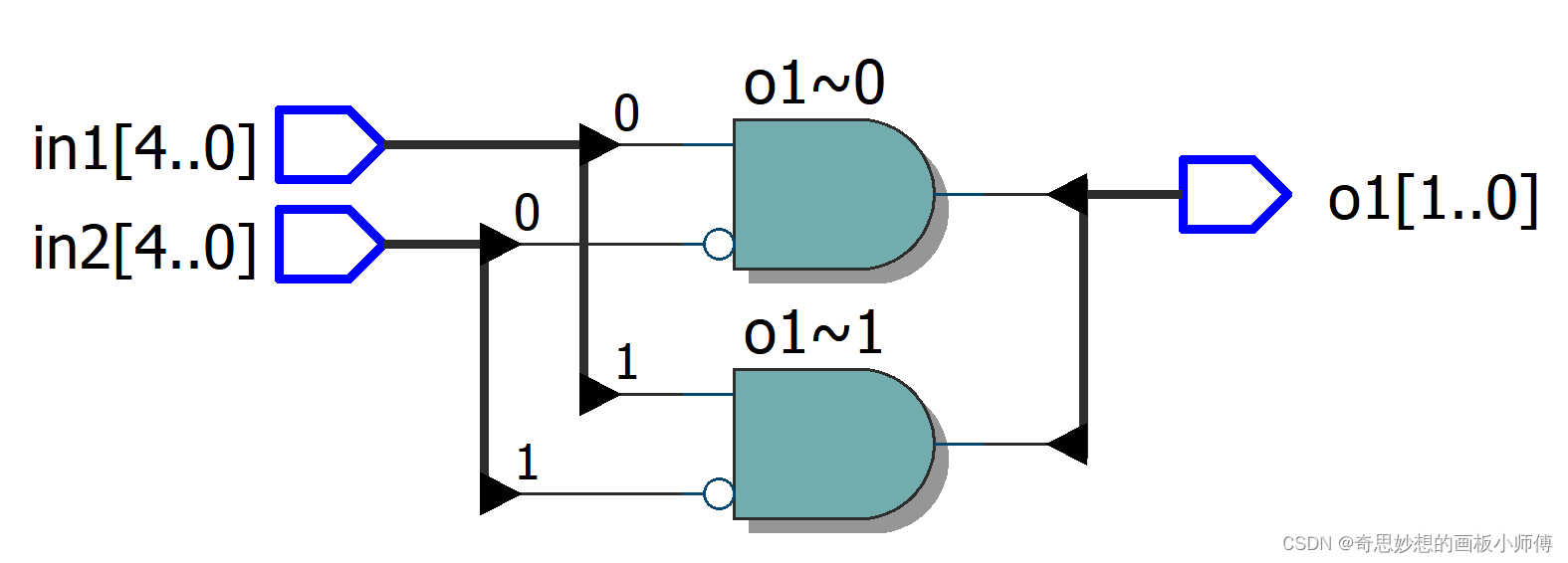

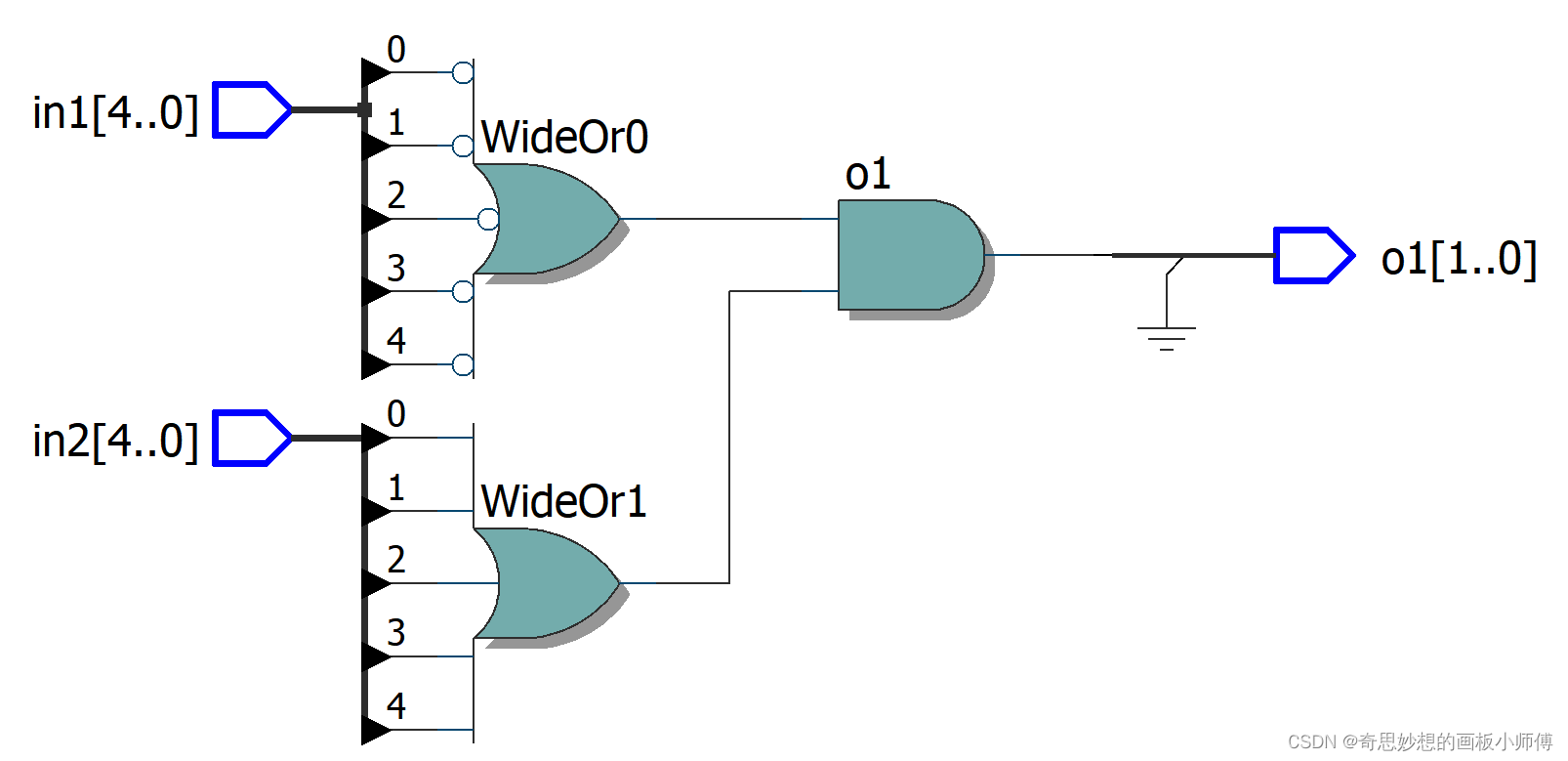

还有同学疑问:多位宽的数之间进行逻辑运算等效电路是怎么样的?

经过quartus综合后为:

电路图解释了一切:先是将每一位进行或运算,这就相当于缩位的或运算,再将结果输入一个两输入的与门; 这就解释了 in1只有每个位都为0时才表示0,其余情况为1,in2同理)

这不等同于每一位相与:

位运算符:&、|、^、~、^~

和逻辑运算符类似,位运算符中 &、|、^、^~ 都为双目运算符,只有 “~”为单目运算符;

和逻辑运算符不同的是,位运算符的核心在于 “按位”

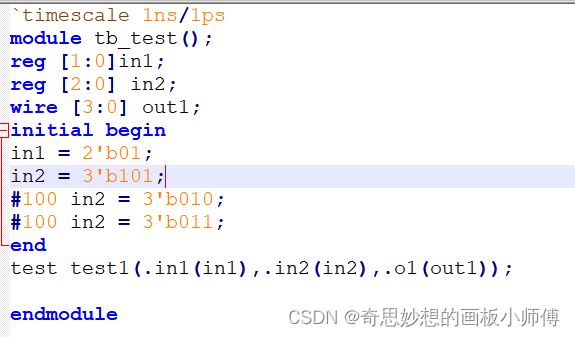

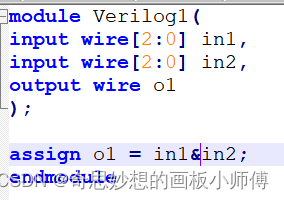

把前面的那个例子做一个小小的修改:

将in1该为两位宽,“&&”替换为“&”

in1恒为 01,in2由 101变为010变为011

这个结果说明了几个事实:

- 位运算是一位对一位的运算(人尽皆知)

- 位运算的两个运算数可以不同长度(in1为2位,in2为3位)

- 位运算是右边对齐的运算,并且缺少的位数将用0补齐(见out1的第三位总是0)

这些结果都在预料之中,主要理论依据是 Verilog的位扩展原则(不足补零)与截断的原则。

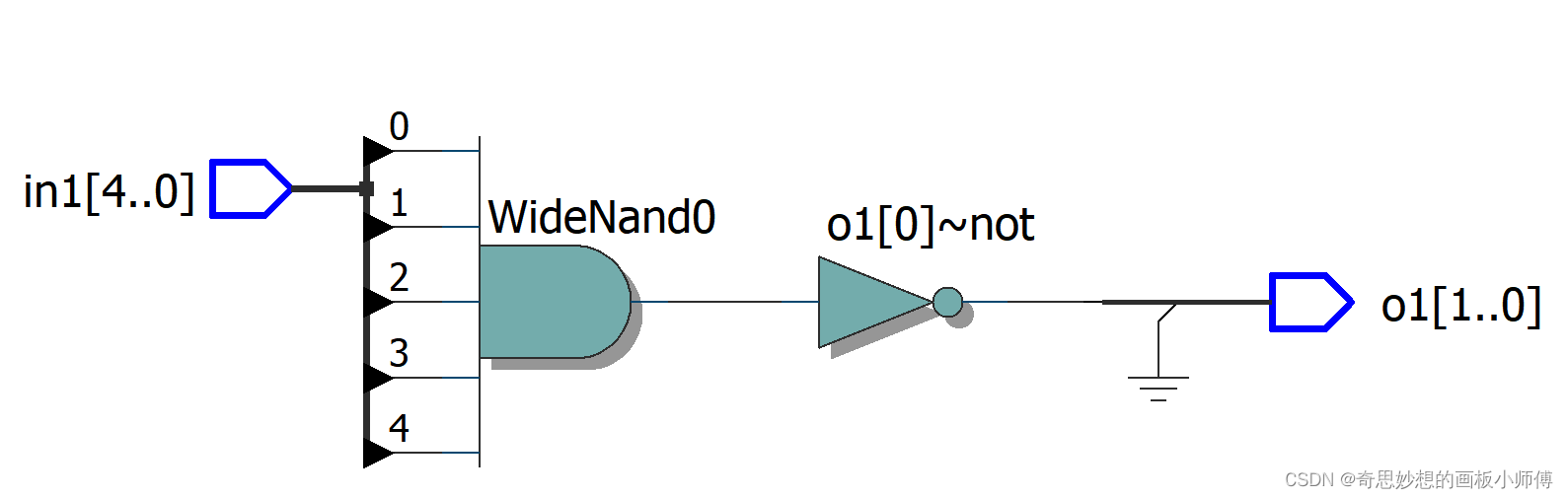

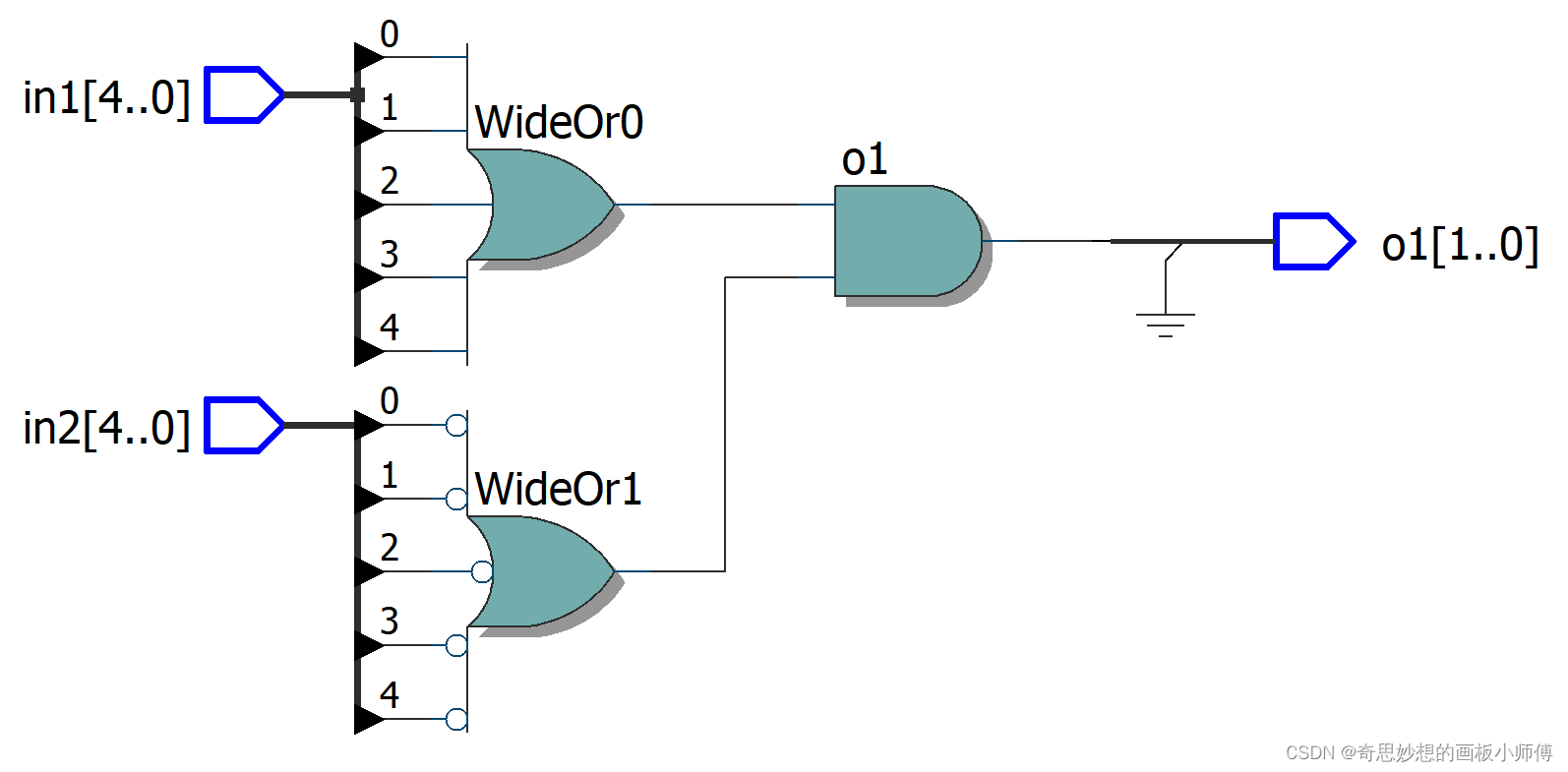

并且,我们来看看综合的结果:

经过quartus综合后为:

可以看到,与逻辑运算符在电路上有明显的不同!

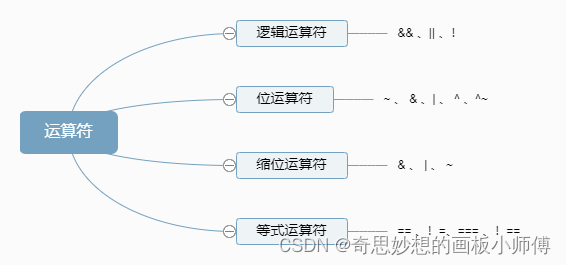

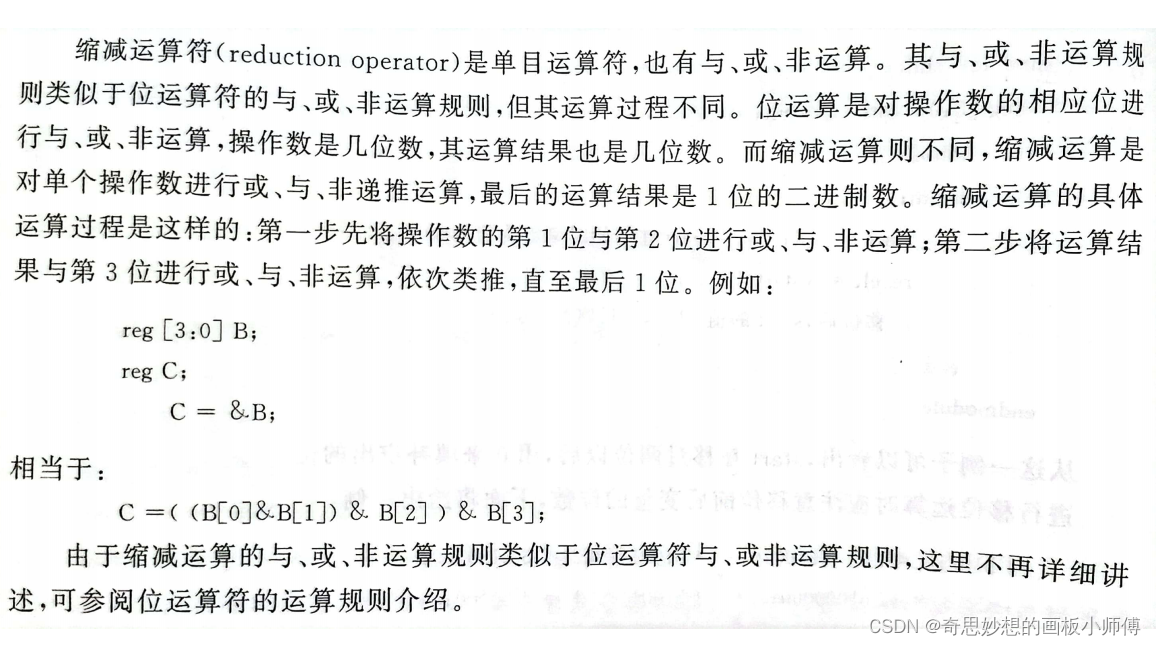

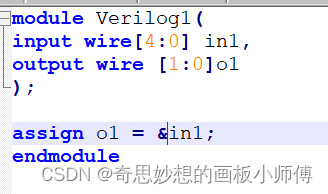

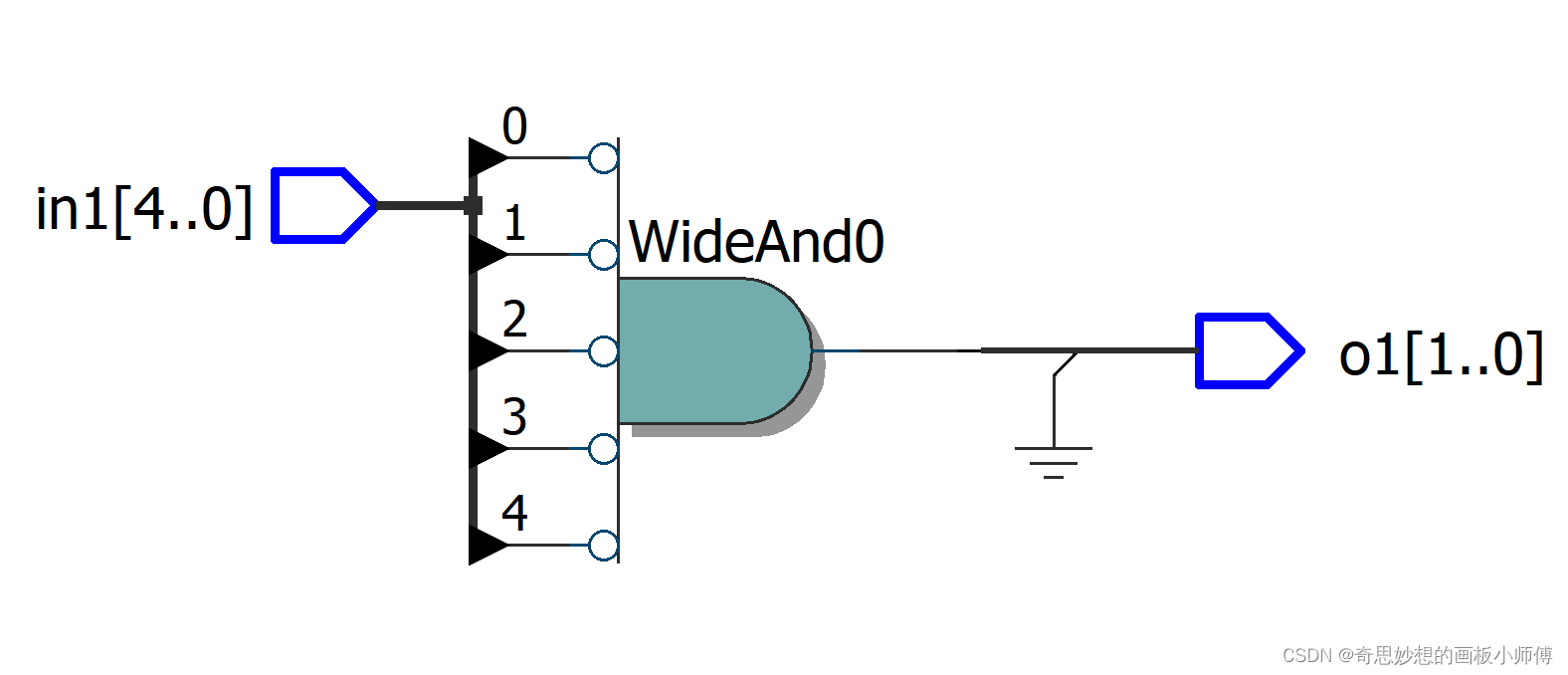

缩位运算符:& 、| 、~、^ 、^~

缩位运算符都是单目运算符,一般是将缩位运算符放置在操作数前面,如 &A、|B、^C、^~D等等,注意千万不要放到后面去,缩微运算和前面讲的逻辑类运算区别度高,我们来看一下其综合的电路有什么特殊之处。

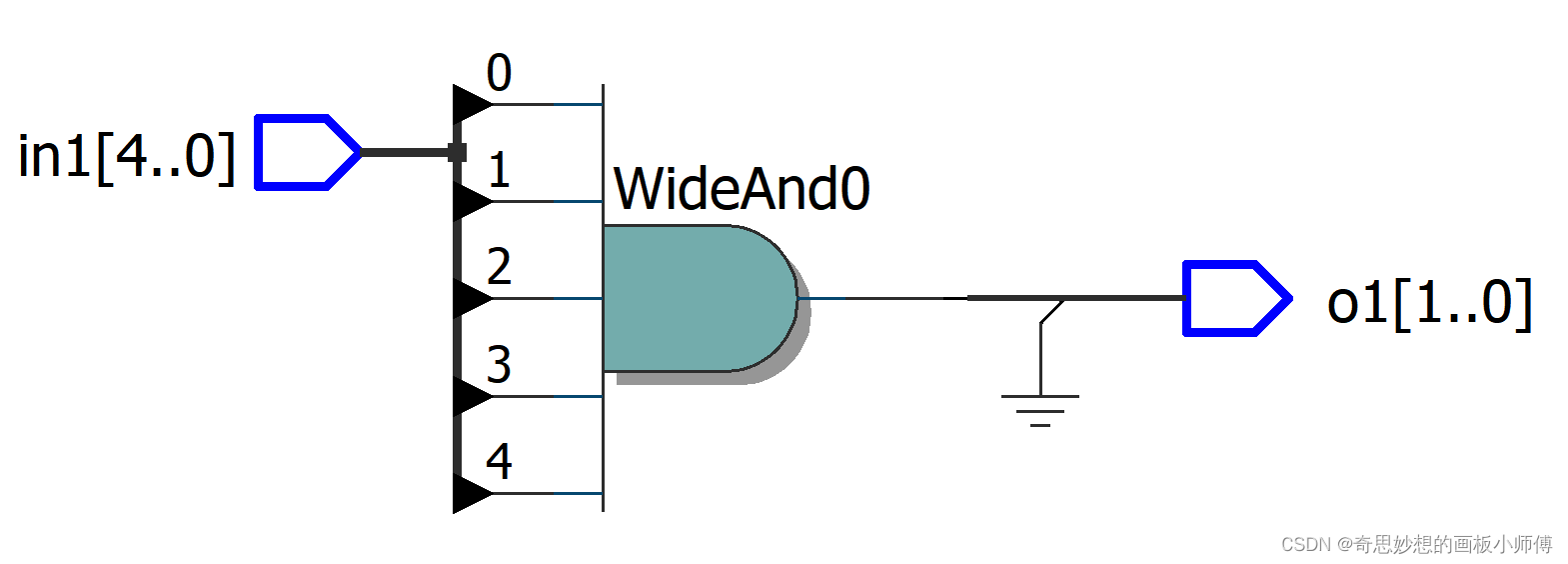

该电路对一个五位宽的输入进行一个缩位操作

可以看到其综合之后的电路图与前两者也不同,是把每一位都当作一个输入进行与操作。

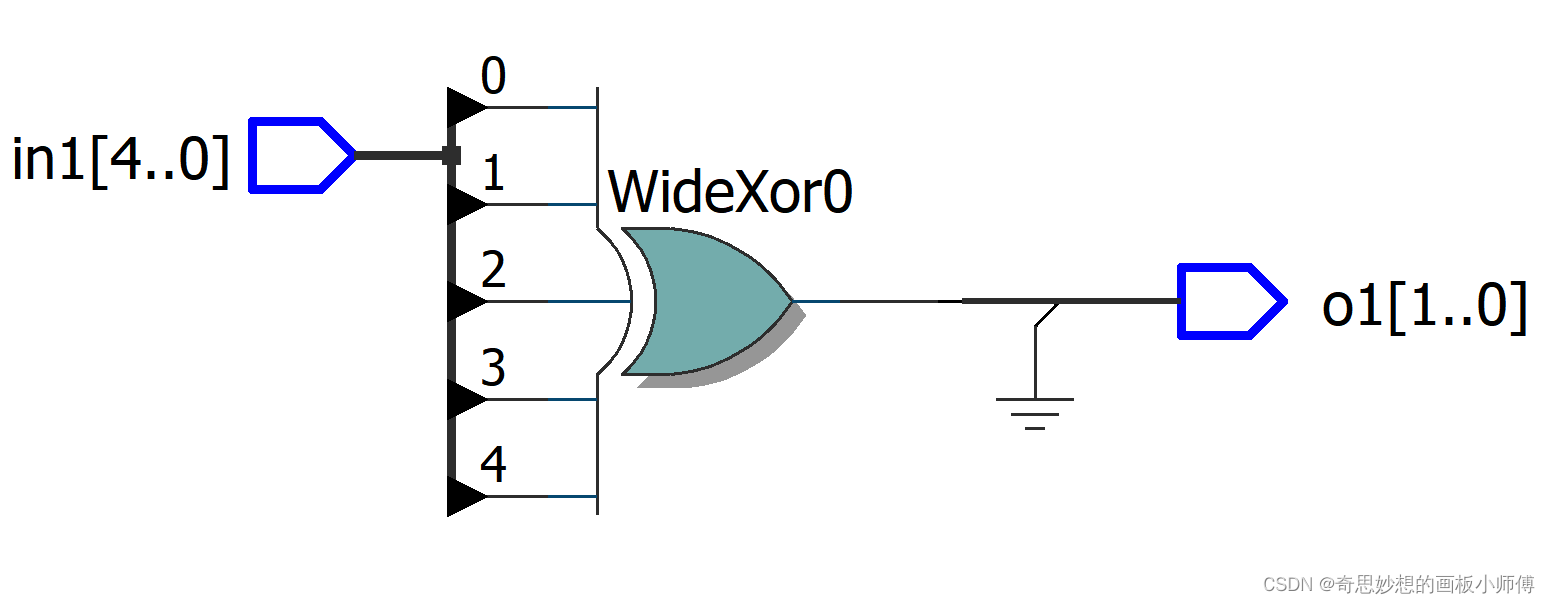

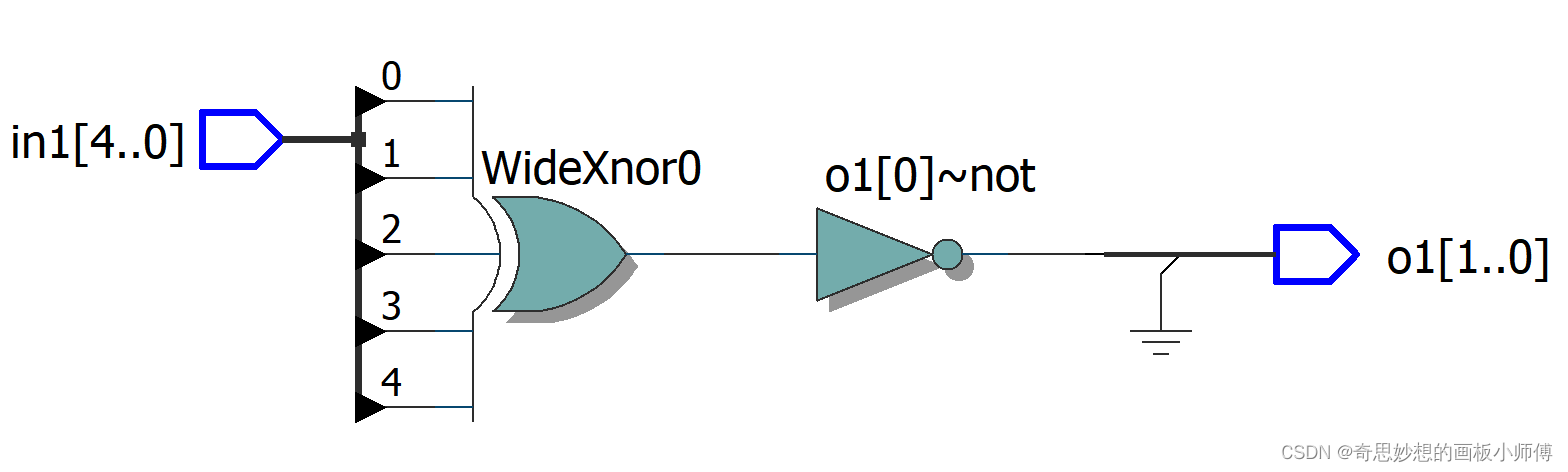

缩位异或:^in1,写这个是因为书上只提了与或非的缩位,其实异或与同或也可以缩位,并且缩位异或常用于奇偶校验。

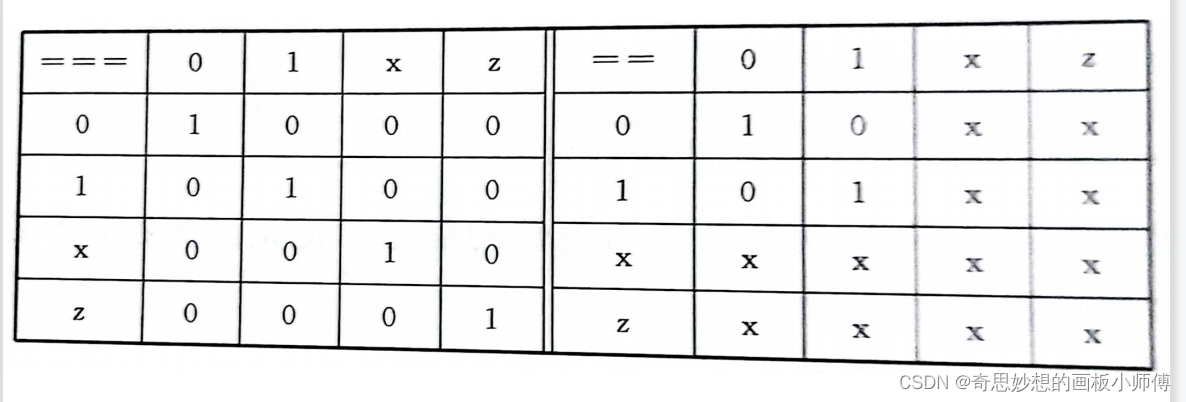

等式运算:== 、!= 、=== 、!==

这个运算的要点就是一个:“===更加严格”

对于比较的数值中有高阻态或者不定态时,==的结果为不定态;

如 “A == 1'b1 ”和 “ A == x ” ,前者即使当A等于x时整体也为x,后者无论A取什么整体都为x;

如“A === 1'bx” 当A等于x时,整体就为1,所以===更加严格,连x和z都比较。

如果不明白的话就看真值表吧:

(你问我这个要怎么看?行列的相交点值就是对应的操作数比较的结果)

奇思妙想

上文把四个容易混淆的运算符都讲解了一遍,总结来说就是:

- 逻辑运算符,要点是真值比较。

- 位运算符,要点是按位比较,位数不够补位(0)

- 缩位运算符,要点是运算符号在操作数前面,结果只有一位

- 等式运算符,要点就是==不能比较高阻Z和不定X,===可以

- A~xxB的形式除了A~^B之外其它的都不行。例如A~&B,A~&&B等形式。

- xx~A:先取A反再 xx ;Axx~B : B取反和A xx; ~AxxB : A取反和Bxx;

练习:

1、A && B是什么运算?

2、&&A 和 !A哪个是对的?

3、A&B是什么运算?和A&&B有什么不同?

4、&A 和~A哪个是对的?

5、A~符合语法吗?

6、^~ 和 ~^效果一样吗?

7、与非是 A&~B 还是~(A&B) ?

8、缩位与非是 ~&A 还是~(&A)?

思路:运算优先级和运算顺序

^~A

^~A

~^A

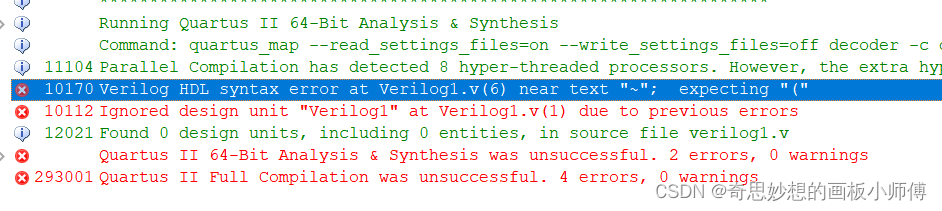

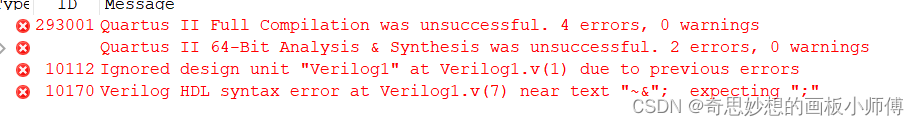

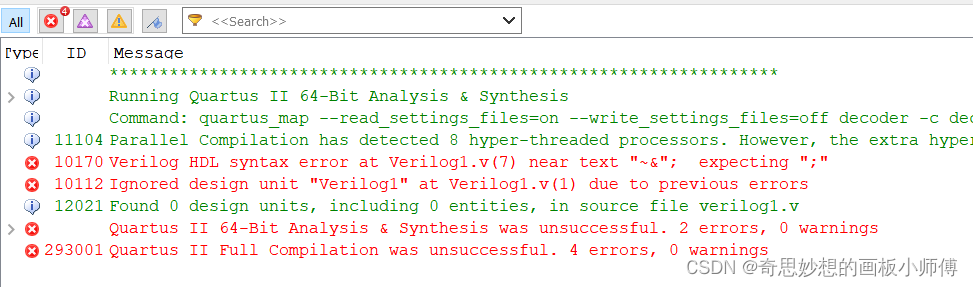

&~A:出现错误

&(~A)就成功了

~&A

A&~B

A~&B:出错

A&&~B

A~&&B:出错

~A&&B

欢迎大家在评论区留下答案!路漫漫其修远兮,吾将上下而求索。

最后

以上就是悦耳学姐最近收集整理的关于浅谈Verilog中的逻辑运算符的全部内容,更多相关浅谈Verilog中内容请搜索靠谱客的其他文章。

发表评论 取消回复