转载自芯司机公众号https://mp.weixin.qq.com/s/_JlLG9y0q4qgSC0xBL2pjw

1.(C)的目的是关注单元模块的集成,功能组合,模块间的接口及时序;sub-chip本身的设计功能和规格正确性。

a. 系统验证(ST)

b. FPGA原型验证

c. 集成验证(IT)

d. 单元验证(UT)

解析:UT(unit test)是模块级别的验证。IT(Integration test)如果集成对象是功能模块,那么属于IP级别的验证,如果集成对象是IP,那么属于子系统级别的验证。ST(Systemtest)是整个SOC级别的验证。

UT侧重单个功能模块及内部RTL实现细节,各个小feature的测试。

IT侧重模块集成,接口信号时序,功能组合的验证,主要运行IP,子系统的一些典型场景用例,debug等用例,来测试sub-chip本身的设计功能和规格正确性。

ST侧重于系统总线,协议,各子系统集成以及功能组合,真实业务场景的测试。

层次从低到高:UT<IT<ST。一般而言UT测过的feature到IT不会再重复测试,UT无法覆盖的才会交给更上一层的IT进行覆盖。ST也是同样道理。如果一个IP里的单元模块出了问题,到IT甚至ST运行更大用例的时候被发现了,那基本上属于很严重的事故,说明前面的测试把关不严,有很大风险。并且由于验证层次的提高,debug难度也增加了。

FPGA原型验证因为FPGA资源有限制,一般来说也是跑一个IP或者是一个小的子系统这个级别的测试,其目的主要是排查一些EDA仿真难以捕获的风险点,并行提高仿真效率,并且可以配合软件的开发,当然也可以发现集成,功能组合的错误,但因为debug困难,需要用chipscope等工具进行信号捕获,信号也不全,因此并不是检查模块功能组合接口时序的主要手段。C是正确的。

- 状态机有冗余状态时,必须有default状态。(正确)

解析:状态机复位之后每个时刻都会处于某个状态。如果one-hot或者binary状态没用满,甚至就算用满了,也需要有一个default状态,用来保证预期之外的错误状态转移(比如亚稳态,glitch)时,能够回到一个稳定的已知状态,减小该预期之外的事件对数据通路造成影响的概率。

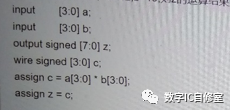

- 以下verilog代码中,a=12,b=10,则z的运算结果为(b)

a. -120

b. -8

c. 120

d. 8

解析:a=4’b1100,b=4’b1010,a*b=7’b111_1000,c=1000=-8, z=1111_1000。

- 在system verilog中,进程之间的同步,不可以采用下面的方法(a)

a. Semaphore

b. Event

c. Mailbox

d. Fork/join

解析:Semaphore是一种线程仲裁结构,并不用于内部事件同步。

- 有符号数右移需要使用哪种操作符(b)

a. >>

b. >>>

解析:两个箭头表示逻辑右移,右移后结果高位补0。三个箭头表示算数右移,右移后结果根据符号位进行拓展。对于无符号数两种表示结果一致。对于有符号数,要用算术右移。

- 下列降功耗措施哪个可以降低峰值功耗(C)

a. Memory shut down

b. 静态模块级clock gating

c. 提高HVT比例

d. Power gating

解析:峰值功耗(peak power)指的是功耗测试用例运行过程中的最大瞬态功耗。也就是说这个时刻的瞬态电流最大。提高HVT比例可以降低工作电流,从而降低峰值功耗。其他三个选项影响的主要是多种场景测试下的平均功耗。

- 测试用例是用来覆盖测试点的,一个用例只能覆盖一个测试点(错误)

解析:用例和测试点不是一一对应的。一个用例可以用来覆盖多个测试点。一个测试点有时候也需要多个用例来覆盖。比如测试FIFO的两个测试点:1.空信号生成 2.满信号生成,使用一个测试用例,在复位之后发出FIFO深度相同数量的写数据,不进行读。一个用例就能同时检测到空信号和满信号覆盖两个测试点。

8.Verilog 语言的层次从低到高依次对应(门级,寄存器传输级,行为级,功能级,系统级)

9.(b)是一种系统验证手段,通过它来判断两个设计是否等价,从而判断一个设计在修改前和修改后的功能是否保持一致。

a. 随机验证

b. 形式验证(formal verification)

c. 网表仿真验证

d. RTL仿真验证

解析:形式验证formality主要应用在:1. RTL与综合网表的比对。因为主要的测试用例都是基于RTL,RTL修改简单,迭代速度快,是一切功能的源头。保证了RTL仿真的正确性加上RTL与网表的形式验证,基本可以保证RTL测试过的测试点在网表阶段没有问题。2. 网表与网表比对:物理实现各阶段网表功能一致性(综合->时钟树->布局布线->TIMING/DRC ECO)。如果有功能ECO,保证ECO之后的网表功能与ECO之前的网表一致也是必不可少的,因为基于网表的修改风险较大,也更不可控,人为确认不够稳。

- 时序收敛的PLL 3分频器的输入时钟与分频后的输出时钟关系是异步时钟(错误)

解析:来自同一个时钟源,并且时序收敛(环路稳定),PLL输入和输出时钟有确定的相位关系(锁相),是同步时钟。

- 使用相同时钟沿的同步数字电路,以下因素和最高工作频率无关的是:(b)

a. 逻辑块间互联布线长度

b. 时钟低电平持续时间

c. 触发器之间的最长组合逻辑

d. 触发器的建立保持时间

解析:对于同步数字电路的最高频率,主要取决于关键路径是否能够收敛,那么就和a,c,d有关系。时钟的低电平持续时间主要影响到时钟信号的有效性。需要做clock pulse width检测,保证该时钟沿能正确地被寄存器采集。如果不满足,则逻辑功能有问题,和最高工作频率无关。

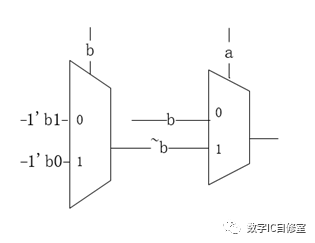

- 只使用2选1的mux实现异或逻辑,最少需要(2)个mux。

解析:这个题目用真值表比较不好做,直接写出异或逻辑的表达式:o=a&~b |~a&b,把a用在mux的sel端,b和非b分别接在mux的2输入则可以实现逻辑。但是考虑到不能用反相器,那么需要用mux再实现一个反向器,将b用在mux的sel端,mux的两个输入分别接1和接0即可。

- 形式验证(formalverification)不存在验证覆盖率的问题,其目的是为了比较两个design的功能,并确认他们的功能是否100%相等。(正确)

解析:形式验证的基本流程是通过切割电路,划分出一系列的比较点。在划分出比较点之后,工具会对两个design的所有比较点进行match,有match不上的点则无法进行比较。然后进行两个design的比较。有比不过的点,则比较失败。因此如果将所有的比较点比较通过作为验证成功的标志,那么需要保证所有的比较点都能match上,并且进行了比较。Formal要求match的比例达到100%,但这里并不存在覆盖率这一说。

- 下面不属于时钟的基本要素是(c)

a. skew(同一时钟源到达不同cell的时间差)

b. clock jitter

c. clock tree(时钟树)

d. clock period

解析:skew+jitter反应在时钟上属于clock uncertainty。Clock period也是时钟的必要要素。以上三者加上setup/hold可以决定一条时序路径的约束。

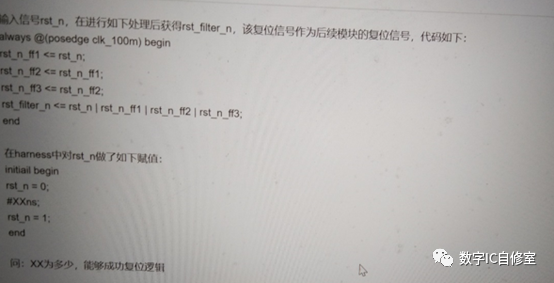

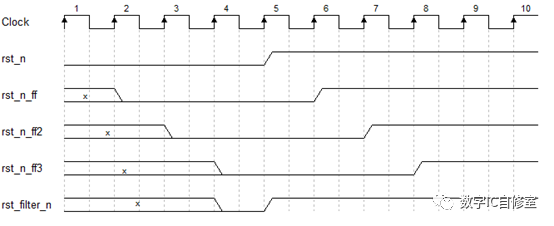

XX为(a)时,能够成功复位逻辑

a. 40

b. 30

c. 20

d. 10

解析:这是一个典型的去除reset抖动的设计。通过输入复位信号打拍做或运算过滤抖动毛刺。因为低电平复位有效,要使rst_n | rst_n_ff1 | rst_n_ff2 | rst_n_ff3产生有效低电平,至少rst_n的低电平时间为4个周期,也就是40ns。

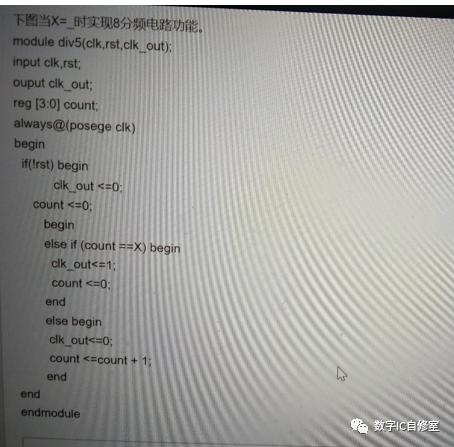

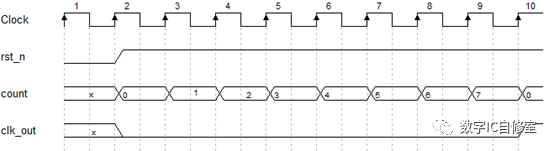

当X=(d)时实现8分频电路功能

a. 2

b. 6

c. 4

d. 7

解析:d,注意到同步复位和寄存器的延迟特性

- 假设输入信号X位宽为12bit,InA位宽为6bit,InB位宽为17bit,实现Y=X*InA+InB的功能,并要求不损失精度,那么输出信号Y的位宽应不小于(c)

a. 29bit

b. 24bit

c. 18bit

d. 15bit

解析:XInA,因为都是输入信号,并且没有类型转换,这里应该默认是无符号数。所以XInA是12+5+1 = 18bit。InB只有17bit,无符号加法高位补0与表达式最高bit的操作数对齐,考虑加法1bit溢出,因此输出信号至少是19bit,这里选c。

- 为保证充分性,随机验证的输入不能带有约束条件,必须使用全随机(错误)

解析:如果全随机,会大量消耗验证机器资源。正确的做法是通过约束条件使随机值落在验证测试点感兴趣的区域,减少无谓的机器资源消耗。

- 下列哪些手段能够降低功耗(a,b,c,d)

a. 操作数隔离

b. 降低频繁开关转换信号的逻辑深度

c. 采降低高翻转信号的负载

d. 减少电路中的glitch

解析:A选项操作数隔离通过减少不必要的操作数计算来降低动态功耗。B选项降低频繁开关转换信号的逻辑深度,实际上也是降低信号toggle的传播,也可以降低动态功耗。C选项通过降低高翻转信号的负载,减少动态翻转产生的电流,依次降低动态功耗。D选项,glitch是无意义的翻转,减少了自然能降低动态功耗。

- 关于FIFO,描述正确的是(a,c,d)

a. 异步FIFO的读写地址通常使用格雷码

b. 同步FIFO的读写地址通常使用格雷码

c. 设计FIFO的重点问题是如何产生读写地址和空满标志

d.FIFO电路主要分为两种,同步FIFO和异步FIFO

最后

以上就是冷静小刺猬最近收集整理的关于2021华为海思实习校招芯片岗真题解析的全部内容,更多相关2021华为海思实习校招芯片岗真题解析内容请搜索靠谱客的其他文章。

发表评论 取消回复