时序约束系列:

- 如何约束时钟

主时钟、虚拟时钟、生成时钟、时钟组、时钟不确定性 - 如何约束输入输出延迟

输入延迟、输出延迟 - 如何约束时序例外

多周期路径、输入输出延迟、虚假路径、最大最小延迟 - 如何约束跨时钟域

总线偏斜

文章目录

- 1 关于CDC约束

- 2 约束总线偏斜(Bus Skew)

- 2.1 关于总线偏斜约束

- 2.2 set_bus_skew 命令的语法

- 2.3 总线偏斜的例子

1 关于CDC约束

跨时钟域(Clock Domain Crossing,CDC)约束适用于具有不同启动(launch)和捕获(capture)时钟的时序路径。

根据启动和捕获时钟关系以及在CDC路径上设置的时序例外(timing exception),分为同步CDC和异步CDC。

例如,被虚假路径(false path)约束覆盖的同步时钟之间的CDC路径是不进行时序分析的,因此被视为异步CDC。

异步CDC路径可以是安全(safe)的也可以是不安全(unsafe)的。异步CDC路径的安全和不安全的术语不同于用于时钟间时序分析的术语(参阅report_clock_interaction)。当异步CDC路径使用一个同步电路,以防止捕获时序单元出现亚稳态时,异步CDC路径被认为是安全的。

可以使用 set_false 或 set_clock_groups 约束完全忽略CDC路径的时序分析,也可以使用 set_max_delay -datapath_only 进行部分分析。此外,可以使用 set_bus_skew 约束约束多bit CDC 路径捕获时间。

2 约束总线偏斜(Bus Skew)

2.1 关于总线偏斜约束

总线偏斜约束用于设置多个异步CDC路径之间的最大偏斜要求。总线偏斜不是与时序路径相关的传统时钟偏斜。相反,它对应于被同一 set_bus_skew 约束覆盖的所有路径上的最大捕获时间差。总线偏斜要求适用于 Fast 和 Slow 边界条件,但未对跨边界条件进行分析。

总线偏斜约束的目的是限制可以 launch数据 并被 单个目标时钟边沿捕获的 源时钟边沿的数量。容差取决于用于受约束路径的CDC同步方案。总线偏斜约束通常用于以下CDC拓扑:

- 格雷码(Gray-code)总线传输,如异步fifo

- 用CE、MUX或MUX保持电路实现的多bit CDC

- 配置寄存器

set_bus_skew 命令可以在 时序已经确保安全的同步CDC上 设置总线偏斜约束,虽然不需要这样的约束。因为 setup 和 hold 检查已经确保了两个安全时序的同步CDC路径之间的安全传输。

总线偏斜约束的CDC场景为:

- 使用

set_clock_groups覆盖的异步CDC - 完全由

set_false_path和/或set_max_delay -datapath_only覆盖的异步CDC - 完全由

set_false_path和/或set_max_delay -datapath_only覆盖的同步CDC

总线偏斜约束不是时序例外;相反,这是一种时序断言(timing assertion)。因此,它不会干扰时序例外(set_clock_group, set_false_path,set_max_delay, set_max_delay -datapath_only, and set_multicycle_path)及其优先级。

总线偏斜约束只能通过 route_design 命令进行优化。要报告 set_bus_skew 约束,请从命令行使用 report_bus_skew 命令或从GUI使用 Reports > Timing > report Bus Skew 命令。总线偏斜约束没有在时序摘要报告(report_timing_summary)中报告。

2.2 set_bus_skew 命令的语法

set_bus_skew [-from <args>] [-to <args>] [-through <args>] <value>

- -from:from选项的对象列表应该是有效startpoint的列表。一个有效的startpoint是一个时钟,一个输入(或inout)端口,或一个时序单元(如寄存器或RAM)的时钟引脚。

- -to:有效的 endpoint ,一个有效的endpoint是一个时钟,一个输出(或inout)端口,或一个时序单元的数据引脚。

- -through:-through选项的节点列表应该是有效的引脚、端口或网表。

注意:

- 在指定总线偏斜约束时,必须同时指定-from和-to选项

- Xilinx建议在没有扇出输出的路径上设置总线偏斜约束。此外,每个总线偏斜约束必须覆盖至少两个起点和两个终点。

总线偏斜值必须是现实的和合理的。Xilinx建议使用大于源和目标时钟最小周期的一半的值。总线偏斜的推荐值还取决于CDC拓扑,如以下示例所示。

2.3 总线偏斜的例子

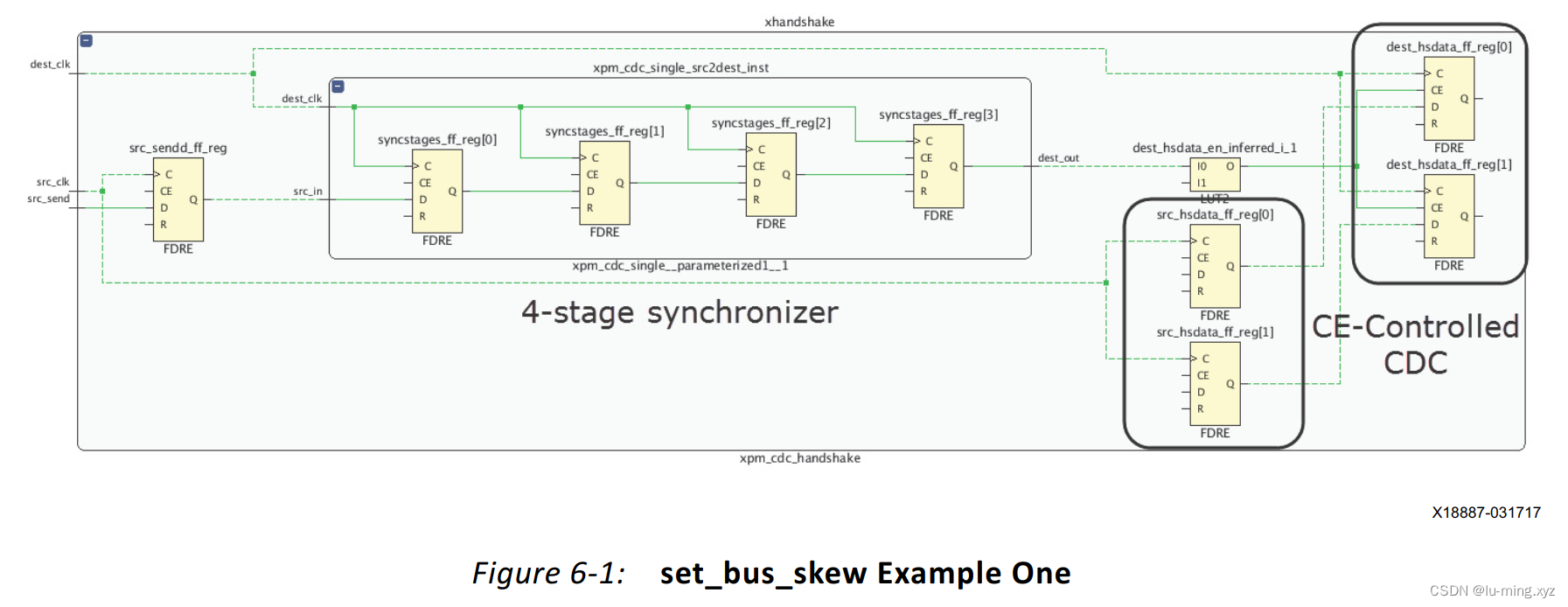

例子1:在本例中,CDC是握手机制的一部分。当数据可用于采样时,源时钟域生成发送信号。目标时钟域对发送信号使用4级同步器。在4级同步器之后,信号驱动CDC目标寄存器的时钟使能(CE)引脚。在这种时钟使能的控制CDC结构中,总线偏斜必须调整为CE路径上的级数,因为它代表数据有效的目标时钟周期数。

当源时钟周期为5ns,目的时钟周期为2.5 ns时,需要将CDC路径上的总线偏斜设置为10ns (4×2.5 ns)。

set_bus_skew -from [get_cells src_hsdata_ff_reg*] -to [get_cells dest_hsdata_ff_reg*] 10.000

注意:为了完整性,CDC需要一个额外的 set_max_delay 约束来确保源寄存器和目标寄存器没有放置得太远:

set_max_delay -datapath_only -from [get_cells src_hsdata_ff_reg*] -to [get_cells dest_hsdata_ff_reg*] 10.000

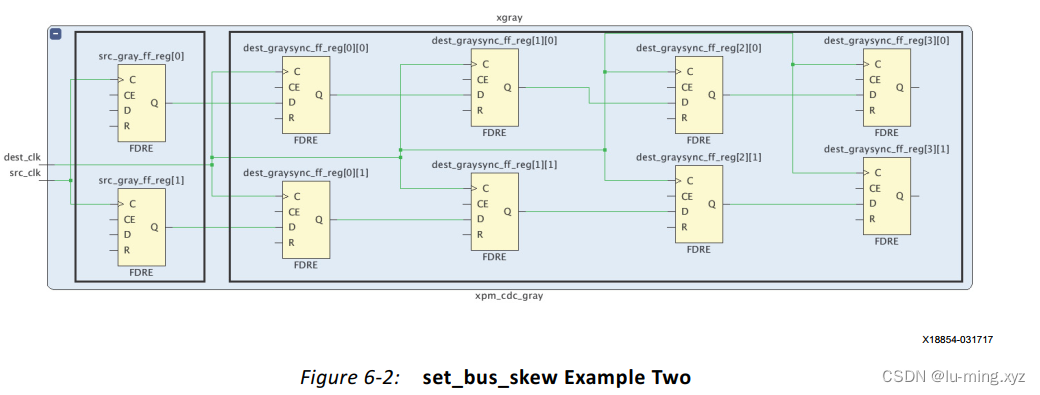

例子2:在本例中,CDC位于格雷码的总线上。系统必须保证目标时钟域在同一时间只捕获格雷码总线的一个转换。

如果源时钟周期为5ns,目标时钟周期为2.5 ns,则CDC路径上的总线偏斜应设置为2.5 ns(目标时钟周期)。

set_bus_skew -from [get_cells src_gray_ff_reg*] -to [get_cells {dest_graysync_ff_reg[0]*}] 2.500

注意:为了完整性,CDC需要一个附加的set_max_delay约束,以确保源和目标寄存器没有放置得太远。在这种情况下,最大延迟设置为源时钟周期,因为CDC处于较慢时钟到较快时钟之间,目标时钟域应该只捕获总线的一个过渡:

set_max_delay -datapath_only -from [get_cells src_gray_ff_reg*] -to [get_cells {dest_graysync_ff_reg[0]*}] 5.000

最后

以上就是冷静小刺猬最近收集整理的关于【ug903】FPGA时序约束学习(4)-如何约束跨时钟域(Clock domain crossing,CDC)1 关于CDC约束2 约束总线偏斜(Bus Skew)的全部内容,更多相关【ug903】FPGA时序约束学习(4)-如何约束跨时钟域(Clock内容请搜索靠谱客的其他文章。

发表评论 取消回复