1 数字电路设计有哪几种层次可否分别举个例子?

答:当前的数字电路设计从层次上可以分成以下几个层次:

① 算法级设计。利用C语言及其他一些系统分析工具如Matlab对设计从系统的算法级方式进行描述。算法级不需要包含时序信息;

② RTL级设计:用数据流在寄存器间传输的模式来对设计进行描述;

③ 门级:用逻辑级的与或非门等门级之间的连接对设计进行描述。

④ 开关级:用晶体管和寄存器及他们之间的连线关系型对设计进行描述。

算法级是高级的建模,一般对特大型设计或有较复杂的算法时使用,特别是通讯方面的一些系统,通过算法级的建模来保证设计的系统性能。在算法级通过后,再把算法级用RTL级进行描述。门级一般适合小型设计,开关级一般是在版图级进行。

2 能否回忆一下在学校中用原理图进行设计的方法或者在数字电路课中进行数字电路设计的方法?能够用HDL语言简单描述一下4位宽的加法器。

(该题答案参考原链接如下:(14 封私信 / 6 条消息) 一个实际电路的原理图是怎样设计出来的? - 知乎 (zhihu.com))

(1)设计电路以实现 某种需求

① 首先需要确定详细的需求,比如要求扬声器最大功率达到10W,放大器失真不超过0.5%,频率在20Hz到20KHz之间等;

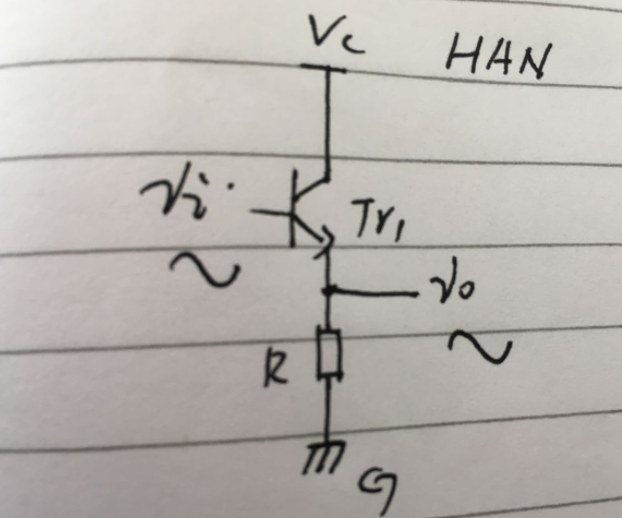

② 而后,根据具体功能进行电路架构设计;如当output 功率为10W时,假设负载电阻为8Ω,频率1KHz,则通过扬声器的电流为1.12A。那么在晶体管的三种基本接法中,只能选择集电极接地电路,如下图所示:

图1 集电极接地电路 图2 共射电路

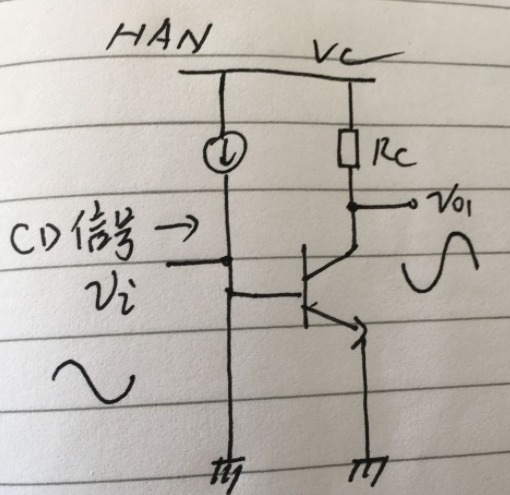

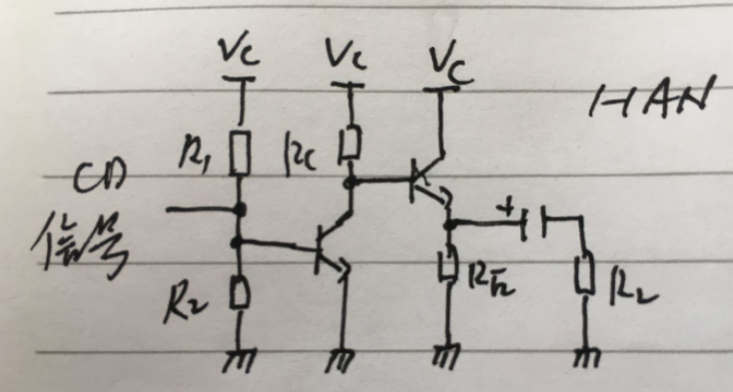

此时电压为1.12*8=8.96V,则需要把CD机出来的音频信号的电压放大到8.96V,此时可以选择共基或共射电路。但由于音源输出电阻较大,而共基电路输入电阻较小,所以只能选择共射电路,如图2所示。则设计后的电路如图3所示。

图3 扬声器电路 图4 调整后的电路图

③ 接下来是对架构进行调整。分析上一步设计的架构存在哪些问题。

比如,上面的架构存在:1 跟随器的空载电流较大,造成发热严重且放大器效率低下;2 输出级使用电容,会和负载形成高通滤波器,处理这一新的问题会增加较多成本且降低电路可靠性; 3 该设计的温漂问题会很严重; 4 该电路会有很大的失真。

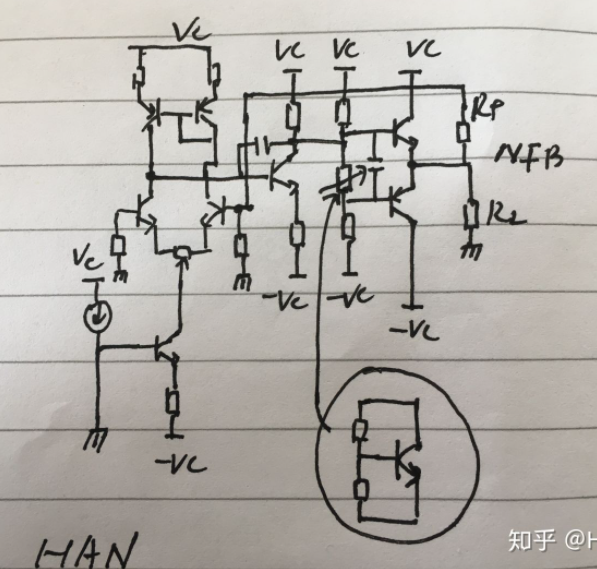

为此,1 对于空载电流大的问题,修正为推挽跟随器电路,同时解决使用输出电容的问题;2 对初级电路使用差动放大电路,改善温漂情况;3 对于失真问题,增加开环增益,然后进行深度负反馈配置,以大幅度降低THD和噪声。调整后的架构图如图4所示。

④ 调整架构后,继续进行具体设计,即确定架构中每一个元器件的具体参数、型号。

设计完毕后会进行仿真,确定原理图无误后输入到AD/EDA等软件进行线路板Layout设计。

(2)用HDL语言简单描述一下4位宽的加法器。

//一个四位宽的加法器(全加器),首先定义一个加法器模块

module adder(a,b,cin,count,sum);

input [3:0] a,b; //定义四位宽的变量a,b表示两个加数

input cin; //表示来自低位的进位

output [3:0] sum; //定义和

output count; //向高位的进位

//4位全加器的逻辑表达式为:count=ab+bcin+acin;sum=a(~cin)+b(~cin)+abcin;

assign{count, sum} = a + b;

endmodule

//也可以采用数据流的方式对全加器进行建模(这是一个三位的例子)

module adder(a,b,cin,count,sum);

input a,b,cin;

output sum, count;

wire S1, T1, T2, T3;

assign #2 S1 = a ^ b;

assign #2 sum = S1 ^ cin;

assign #2 T3 = A & B;

assign #2 T1 = A & Cin;

assign #2 T2 = B & Cin;

endmodule

//结构化建模,四位全加器通过调用四个一位全加器来实现

module FA_struct(A,B,Cin,Sum,Count);

input A,B,Cin;

output Sum,Count;

wire S1,T1,T2,T3;

xor x1(S1,A,B);

xor x2(Sum, S1, Cin);

and A1(T3, A, B);

and A2(T2, B, Cin);

and A3(T1, A, Cin);

or O1(Cout, T1, T2, T3);

endmodule

module four_bit_FA(FA, FB, FCin, FSum, FCount);

parameter SIZE=4;

input [SIZE:1]FA;

input [SIZE:1]FB;

input FCin;

output [SIZE:1] FSum;

output FCout;

wire FTemp1,FTemp2,FTemp3;

FA_struct FA1(

.A(FA[1]),

.B(FB[1]),

.Cin(FCin),

.Sum(FSum[1]),

.Cout(Ftemp1)

);

FA_struct FA2(

.A(FA[2]),

.B(FB[2]),

.Cin(Ftemp1),

.Sum(FSum[2]),

.Cout(Ftemp2)

);

FA_struct FA3(

.A(FA[3]),

.B(FB[3]),

.Cin(Ftemp2),

.Sum(FSum[3]),

.Cout(Ftemp3)

);

FA_struct FA4(

.A(FA[4]),

.B(FB[4]),

.Cin(Ftemp3),

.Sum(FSum[4]),

.Cout(FCout)

);

endmodule3 当前两种硬件描述语言是什么?

Verilog, VHDL

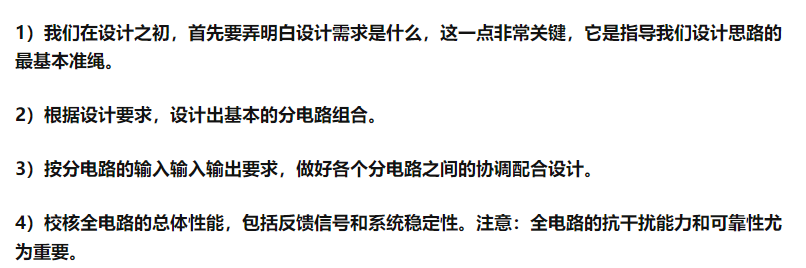

4 以CPU为例,能否画出Top-Down的树状图?

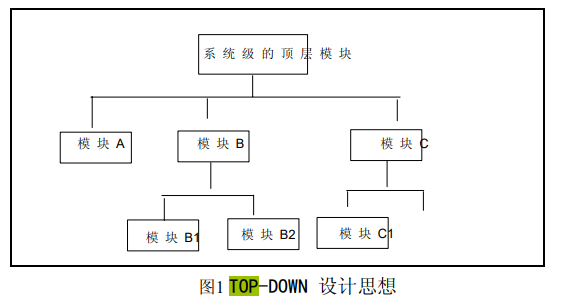

5 假设一触发器组的器件Reg8,输入信号Din, 输出信号Qout, 位宽为8位,时钟信号Clk, 异步复位信号Rst,用于实现对8位数据总线的寄存,描述出module语句,并画出电路的示意图。

module Reg8(Din, Qout);

input Clk;

input Rst;

input [7:0] Din;

output [7:0] Qout;

always@(posedge Clk or negedge Rst)

Qout <= Din;

endmodule6 HDL有哪几种建模方式?

在HDL的建模中主要有:结构化建模方式、数据流描述方式和行为描述方式。其中,

结构化建模方式:通过对电路结构的描述来建模,即通过对器件的调用并使用net连接各器件的描述方式;

数据流建模方式:通过对数据流在设计中的具体行为的描述来建模,最基本的机制是使用连续赋值语句assign,将某个值赋给某个wire型变量;也需要借助于HDL提供的一些逻辑运算符。

行为建模方式:采用对信号行为级的描述的方法,在表示方面类似于数据流的建模方式,一般是把用initial块语句或always块语句描述的归为行为建模方式。行为建模方式需要借助一些行为级的运算符如+-等。

7 结构化建模方式的主要语句是什么? .A(A)的两个A具体含义是什么?

xor,or,and 异或门,或门,与门。

.A(A)

.A表示调用器件的管脚A,括号中的A表示接到该管脚A的电路中的具体信号。

8 数据流的建模方式采用什么语句?语法是什么?

数据流的建模方式采用连续赋值语句,语法为:

assign [delay] net_name = expression;

如 assign #2 A = B;

9 行为建模方式采用什么语句?信号的数据类型必须是什么?

行为方式建模采用initial块语句或always块语句。信号的数据类型必须是寄存器reg型.

10 简单介绍一下串行语句和并行语句的概念。

串行语句又称顺序语句,顺序语句的执行与语句所在的位置有关,顾名思义按照时序一句一句执行指令,在上一句结束之后才开始下一句的执行;而并行语句语句之间没有联系,可以在同一时刻同时执行。

VHDL中,顺序语句用于行为描述,不能直接置于结构体中,用于描述子函数;并行语句用于数据流描述或者结构描述,在结构体中的每一个并行语句,都描述了一个功能块,并行语句不描述顺序,结构体中的并行语句可以按照任何顺序书写。

11 Verilog HDL中规定了哪四种基本值类型?

Verilog HDL中规定了四种基本的值类型:

0:逻辑0或假;

1:逻辑1或真;

X:未知值;

Z:高阻。

12 写出下面整型数值的二进制表示:5'O37, 4'D2, 8'h2A, 7'Hx, 5'H7F

(这个后面看了语法基础之后再进行核对)

5‘O37: 5位的八进制数 3*8^1+7*8^0=31 二进制5'b11111

4'D2: 4位的十进制数 2 二进制4'b0010

8'h2A 8位的十六进制数 2*16^1+10*16^0=32+10=42 二进制8'b00101010

13 有哪几种主要的数据类型?可否说明它们的简单用法?

Verilog HDL主要包括两种数据类型:线网类型(net type)和 寄存器类型(reg type)

线网类型(wire普通线网,tri三态线网)用于对结构化器件之间的物理连线的建模;如器件的管脚,内部器件的输出等;

寄存器类型(reg)用于对存储单元的描述,如D型触发器、ROM等。此外,在always语句中进行描述的必须用reg型变量。

14 initial 语句和always语句的区别是什么?可否用语句产生一个周期20ns的方波,初始值为1,产生一个复位信号rst,0-40ns为1,之后保持0.

initial语句只执行一次,即在设计被开始模拟执行时开始。通常只用在对设计进行仿真的测试文件中,用于对一些信号进行初始化和产生特定的信号波形。

always语句与initial语句相反,是被重复执行,执行机制是通过对一个称为敏感变量表的事件驱动实现。

initial

Clk = 1;

Rst = 1;

always //重复执行

#10 Clk = ~Clk; //初始值为1,周期为20ns的方波

#40 Rst = 0; //0-40ns保持初始值为1,之后保持0.

最后

以上就是哭泣西装最近收集整理的关于华为Verilog入门教程后习题解答的全部内容,更多相关华为Verilog入门教程后习题解答内容请搜索靠谱客的其他文章。

发表评论 取消回复