想偷懒用Simulink仿真成功的模型直接生成Verilog代码,但在这世界上偷懒似乎是没有好结果的。

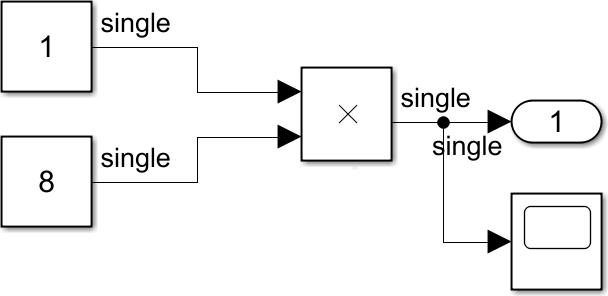

生成的Verilog代码繁多不说,结果也是匪夷所思。后来,我干脆简化到极致:把1*8用Simulink的乘法模块product来实现再生成Verilog代码,simulink模型如下:

结果应该是8。但自动生成的Verilog代码却是:

module mult1009

(Out1);

output [31:0] Out1; // single

wire [31:0] Product_out1; // ufix32

assign Product_out1 = 32'h41000000;

assign Out1 = Product_out1;

endmodule // mult1009很简单的,没有输入只有输出,但结果却是 32'h41000000。8的二进制形式只有1个1呀,但这个32位的序列中却有41=0100 0001,一共有两个1,百思不得其解。其它的奇葩现象还有:

6转成32'h40c0 0000;2转成32'h4000 0000;4转成2'h4080 0000。Quartus给出的仿真结果都是很大的数。

只有输出0是对的,等于32'h0000。

结论:不偷懒,扎扎实实编Verilog代码实现小数乘法。

期待:高能的看客指出问题,给出意见。在此先道谢了。

最后

以上就是大力猎豹最近收集整理的关于Matlab/Simulink模型自动生成Verilog代码出现的异常现象的全部内容,更多相关Matlab/Simulink模型自动生成Verilog代码出现内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复