SIMULINK模型自动生成Verilog代码的关键,主要有两部分:1、Verilog代码生成方法。2、根据芯片实际可用资源调整模型结构。其中第二点尤为重要,笔者之前曾因为模型生成的代码过多,超过芯片可用资源而导致程序在芯片上编译失败。接下来我从这两方面来介绍Verilog自动生成。

一、Verilog代码生成方法

1、代码生成前参数设置

在使用HDL Coder转换代码之前,需要对一些参数和环境进行设置,保证后续Verilog代码正常生成。

使用HDL Coder转换代码需要先将待转换模型封装为一个系统,具体做法是,选中全部待转换部分,单击鼠标右键,点击Create Subsystem from Selection,即可生成一个Subsystem,双击名称,即完成封装。

此外,还需要配置模型参数。在Simulink的主页面点击Simulation,点击Model Configuration Param,进行参数配置。首先选中Solver,将Simulation time仿真时间的Stop time设置为10,将Solver options的Type设置为Fixed-step,将Solver设置为discrete(no continuous states),然后点击Hardware Implementation,将Device vendor设置为ASIC/FPGA,最后点击OK保存,至此完成模型参数配置。

2、关联编译软件

HDL Coder代码生成需要结合具体的FPGA编译软件,这就需要Simulink与PFGA编译软件进行关联。在MATLAB中运行如下命令:hdlsetuptoolpath ('ToolName','Xilinx Vivado','ToolPath','E:XilinxVivado2018.3binvivado.bat')。其中ToolName是代码编译的工程软件,Xilinx的编译软件有ISE、Vivado等,具体的软件还需要根据具体的开发板确定。本文使用Vivado编译软件。ToolPath是编译软件的安装路径,其它具体信息可以参考hdlsetuptoolpath的帮助文档。

3、HDL Coder代码生成

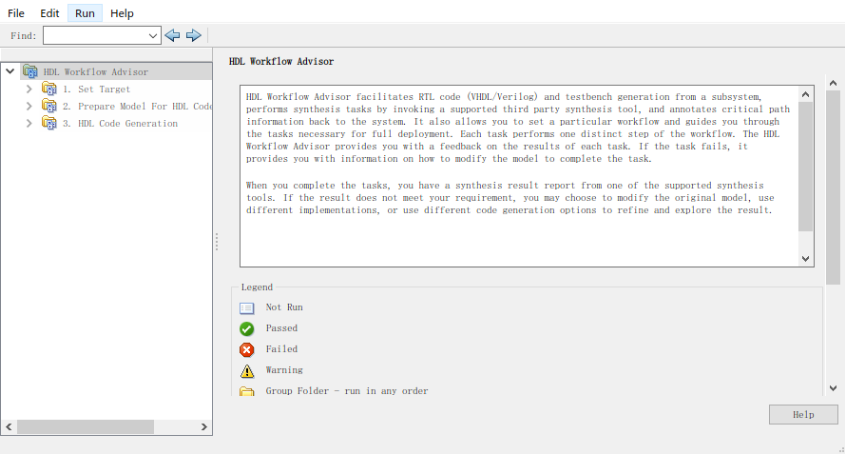

完成上述设置后,点击Simulink主页面上的Code,在弹出小窗中点击HDL Code,再选择HDL Workflow Advisor。之后会弹出一个System Selector的窗口,需要在这里选择代码转换的模型系统。打开待转换模型所在总文件,选择待转换模型,点击OK,等待片刻之后,便打开了HDL Coder代码生成的HDL Workflow Advisor窗口,如图 1所示。整个进程分为3个部分,分别是设定目标、为HDL代码生成准备模型以及HDL代码生成。第一部分主要是对将要生成的一些代码进行参数设定,包括开发板型号,时钟频率等等;第二部分是生成用作代码转换的模型;第三步是根据模型生成代码。若要得到可用的Verilog代码,需要完整通过这三个进程。

图1

首先双击Set Target,点击Set Target Device and Synthesis Tool,打开界面,在这里选择程序编译软件以及具体的开发板,用于分析开发板可用资源是否够用。在右边Synthesis tool处,选择仿真软件;在Family、Package和Speed处选择目标芯片的参数;在Project folder处修改至指定项目工作夹,最后点击Run This Task。完成这一步后,页面左侧会出现第四部分,是关于FPGA综合与分析,分析该开发板资源情况是否符合要求。

之后是1.2 Set Target Frequency,在这里设置目标频率。根据开发板的资料,设置时钟频率,设置完成后,点击Apply,点击Run This Task,完成频率设置。

第二部分Prepare Model For HDL Code Generation是为HDL代码生成准备模型,没有需要特别设置的地方,只需要右击标题,点击Run All即可。

第三部分是HDL代码生成,在这里需要对生成的代码做进一步要求。3.1是设置代码生成选项,在Set Basic Options中,主要是设置生成的语言形式,本文是基于Verilog开发的,故选择Verilog。Set Advanced Options是进行一些高级设置,在此处,要注意将Reset asserted level设置为Active-low,表示复位信号采用低电平有效,其余设置默认即可。Set Optimization Options部分为优化设置,这里不需要特别修改,默认即可。3.1.4的Set Testbench Options是设置仿真测试的选项,点击打开后,在Test Bench Generation Output中,勾选HDL test bench和Cosimulation model,其余默认不用修改,点击Apply即可。3.2是生成RTL代码和测试台,打开后在Input Paramenters中勾选Generate RTL code和Generate test bench,然后点击Apply。3.3. Verify with HDL Cosimulation不需要设置修改。最后右键点击3. HDL Code Generation,选择Run All即可。此处需要几分钟的运行时间,完成后已经生成了Verilog代码,可选择相应文件打开。若3.3处出现报错如‘Failed Cannot connect to 'ModelSim' HDL simulator.’,是因为Simulink没有与Modelsim建立联系,在这里直接选择Skip this task,再重新Run This Task,直接忽略错误即可。

第四步是FPGA综合与分析,用于验证生成的代码的具体资源占用情况,并与开发板可用资源做对比,验证该开发板能否完成代码的正常运行。此处不需要进行特殊设置,直接鼠标右键点击4.FPGA Synthesis and Analysis,选择Run All即可。此处分析时间较长。

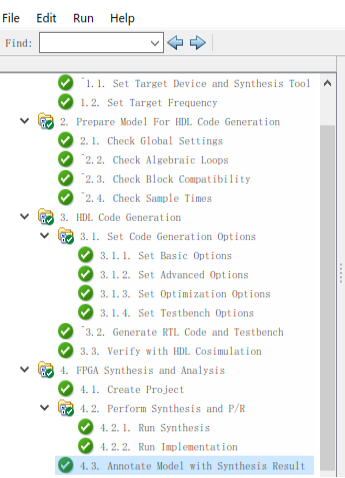

HDL Coder代码自动生成的过程中,需要左侧四个部分全部出现绿色标记,表示顺利完成代码生成以及开发板资源情况分析。如果只完成到第三步,而在第四步报错,则表示Verilog代码已经生成,但是步骤一选定的开发板不能实现代码编译,需要对模型再次调整。当左侧各项全部通过后,具体如图2所示,则表示HDL Coder代码转换全部完成。此时可返回到前文设置的代码生成文件夹,打开工程文件,可以看到模型转换后的Verilog代码。

图2

二、模型结构调整

模型代码转换失败,通常是因为数据类型、程序包过大引起的,现在开始介绍这方面问题的解决办法。

1、模型输入输出接口调整

笔者发现,在模型(特别是复杂模型)转换生成代码后后,模型内部程序代码可读性很差,因此一定要合理设置模型的输入输出,后续调用程序时,只需要给定输入,获取输出即可,这方面因要求而已,就不再赘述。

2、数据格式调整

模型中的数据格式直接影响到模型的代码转换,因此也需要做出细致调整。首先需要在Simulink的主页面中,点击左上角的Display,再点击Signal & Ports,选中Signal Dimensions,以显示传输过程中数据的长度;再点击Display、Signal & Ports,选中Port Data Types以显示具体的数据类型,方便后续观察数据类型并依此进行调整。

在模拟输入信号部分,因为使用MATLAB Function无法调整数据输出格式,默认输出为Double型,为此使用Data Type Conversion模块对数据格式强制转换。双击打开Data Type Conversion模块,将输出数据格式Output data type设置为fixdt(1,16,0),将数据总长度Word length设置为32位,将小数部分长度Fraction length设置为16位,并在末尾选中Saturate on integer overflow,点击OK即可。这样,输出数据就被调整为32位,其中1个符号位,16个小数位。

对于Gain模块,将Signal Attributes中的Output data type和Parameter Attributes中的Parameter data type的数据类型也按照Data Type Conversion中的设置方法进行调整,还包括其他模块的Output data type,都按照这样的格式进行调整。

3、模型计算量调整

调整模型的整体计算量是笔者的一大难点,在生成代码的过程中,在很长一段时间内都出现了需求资源超过开发板可用资源的情况。如何在保证精度的情况下,尽量减小整体计算量以适应开发板完成模型算法,这就需要对模型进行多处调整。

第一,预估数据大小,调整数据位数大小。对于输入数据,这里使用的是AD采集到的数据。根据AD的电压采集范围,笔者使用的AD电压范围是-5~5V,因此整数部分最大为5。根据这一特点,整数部分只需要3位便可达到最大为7的表示范围,因此,将Data Type Conversion输出数据格式调整为20位,其中16个小数位。而对于Constant中的数据,最大为19.5,因此需要5个整数位,将输出数据格式调整为22位,其中16个小数位。同理,经过计算,其他部分的数据的整数位都不超过7,为此,其他数据输出全部调整为20位,其中16个小数位。

第二,模型中尽量不要用到根号。笔者也不清楚FPGA中的运算方式,为了防止增大计算量,所有根号都使用小数表示,精确到6位小数即可。还需要注意的是,常数模块Constant中的Sample time默认为Inf,表示采样时间为无穷大,不满足FPGA资源有限的条件,因此,此处将其设置为2即可。

第三,模型中若有三角函数计算,更需要做调整。对于Trigonometric Function形式的三角函数,它采用迭代的方式进行计算,默认进行11次迭代运算。但是运算量极大,远远超过开发板的可用资源。如果将迭代次数减小到足够小以至于能够完成代码转换的时候,它的精度变得很差,为此,这个三角函数模块不能使用。之后,笔者尝试过根据泰勒展开式,自己使用基础模块搭建模型计算三角函数,但计算量更大,无法满足条件。后来采用查表法,使用Sine HDL Optimized和Cosine HDL Optimized模块,将Number of data points设置为64点,将Table data type设置为fixdt(1,16,0),将数据总长度Word length设置为19位,将小数部分长度Fraction length设置为16位,点击OK保存。

至此,笔者模型修改已经完成,成功生成代码。

以上就是笔者之前使用HDL Coder时积累到的经验和方法。鉴于笔者能力有限,若有错误可在评论区指出,感谢各位的支持和理解。

最后

以上就是动听小霸王最近收集整理的关于SIMULINK模型自动生成Verilog代码的全部内容,更多相关SIMULINK模型自动生成Verilog代码内容请搜索靠谱客的其他文章。

发表评论 取消回复