实验目的: 以计数器为例学会简单的时序逻辑电路设计

实验平台: FPGA开发板

实验原理

时序逻辑电路是指电路任何时刻的稳态输出不仅取决于当前的输入,还与前一时刻输入 形成的状态有关。这跟组合逻辑电路相反,组合逻辑的输出只会跟目前的输入成一种函数关 系。换句话说,时序逻辑拥有储存元件(内存)来存储信息,而组合逻辑则没有。

计数器的核心元件是触发器,基本功能是对脉冲进行计数,其所能记忆脉冲最大的数目 称为该计数器的模/值。计数器常用在分频、定时等处。计数器的种类很多,按照计数方式的 不同可以分为二进制计数器、十进制计数器以及任意进制计数器,按照触发器的时钟脉冲信 号来源可分为同步计数器与异步计数器。按照计数增减可分为加法计数器、减法计数器以及 可逆计数器。

此处设计一个计数器,使其使能板载LED 每500ms,状态翻转一次。核心板晶振为50MHz, 也就是说时钟周期为 20ns,这样可以计算得出 500ms = 500_000_000ns/20 = 25_000_000;即 需要计数器计数 25_000_000 次,也就是需要一个至少 25 位的计数器。且每当计数次数达到 需要清零并重新计数。

计数器Verilog实现

module counter(clk50M,Rst_n,led)

//接口定义

input clk50M; //系统时钟50M

input Rst_n; //低电平复位

output reg led; //输出;

reg[24:0]cnt;

//计数器计数进程

always@(posedge clk50M or negedge Rst_n)

if(Rst_n==1'b0)

cnt<=25'd0;

else if(cnt==25'd24_999_999)

cnt<=25'd0;

else

cnt<=cnt+1'b1;

//led输出进程

always@(posedge clk50M or negedge Rst_n)

if(Rst_n==1'b0)

led<=1'b1;

else if(cnt==24'd24_999_999)

led=~led;

else

led<=led;

endmodule

激励仿真及仿真测试

`timescale 1ns/1ns

`define clock_period 20

module counter_tb;

reg clk;

reg rst_n;

wire led;

counter counter0(

.Clk50M(clk),

.Rst_n(rst_n),

.led(led)

);

initial clk = 1;

always #(`clock_period/2) clk = ~clk;

initial begin

rst_n = 1'b0;

#(`clock_period *200);

rst_n = 1'b1;

#2000000000;

$stop;

end

endmodule

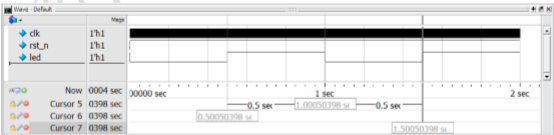

设置好仿真脚本后进行功能仿真,可以看到波形文件,可以看出高低电 平变化的时间均是 0.5s 也就是 500ms,得出符合既定的设计要求,至此功能仿真结束。

最后

以上就是洁净板凳最近收集整理的关于时序逻辑电路设计___计数器的全部内容,更多相关时序逻辑电路设计___计数器内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复