从零开始的FPGA学习6-计数器

- 加法计数器

- 原理

- 代码

- 仿真

- 波形

- RTL

- 减法计数器

- 原理

- 代码

- 仿真

- 波形

- RTL

- 结束语

加法计数器

原理

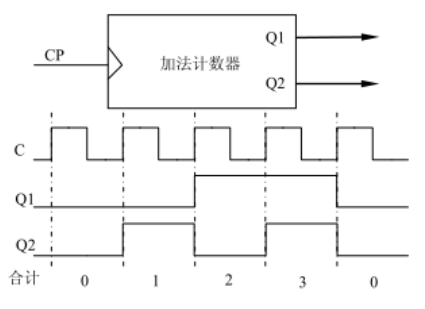

每次时钟脉冲信号 clk 为上升沿时, 计数器会将计数值加 1。下图为模4计数器。

代码

module lab(

input clk,

output reg [3:0]Q=0 //模16计数器

);

always @(posedge clk)

begin

Q<=Q+1;

end

endmodule

仿真

module Test();

//input

reg clk;

//output

wire [3:0]Q; //不要漏掉[3:0],否则仿真有误

initial

begin

clk=0;

end

always #50 clk=~clk;

lab test(

.clk(clk),

.Q(Q)

);

endmodule

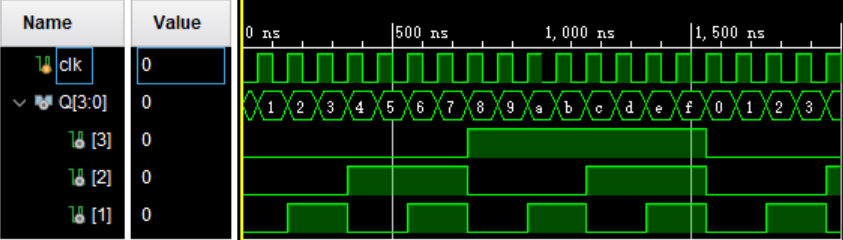

波形

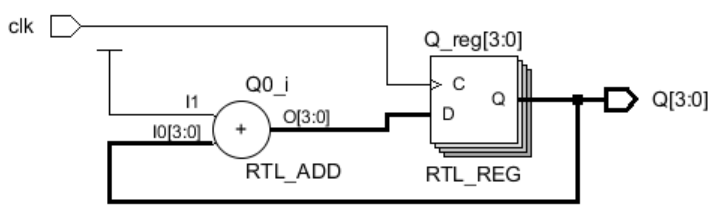

RTL

减法计数器

原理

减法计数器的计数方式改成 15,14…0,其他与加法计数器一样

代码

module lab(

input clk,

output reg [3:0]Q=4'b1111 //模16计数器

);

always @(posedge clk)

begin

Q<=Q-1;

end

endmodule

仿真

和加法计数器一样

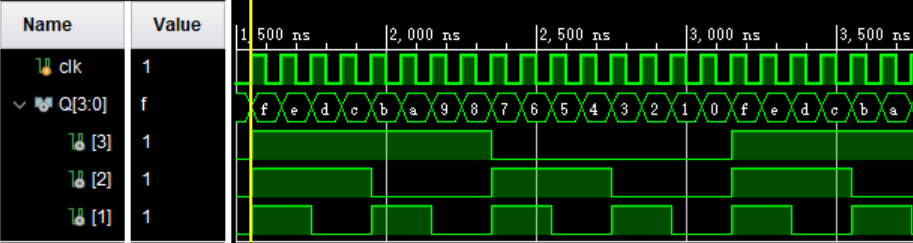

波形

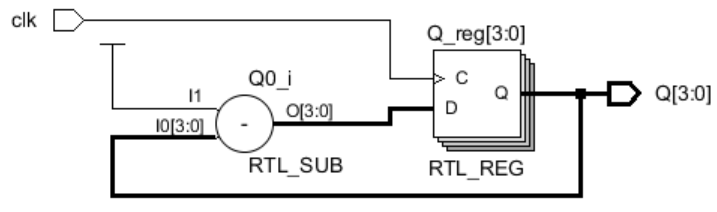

RTL

结束语

这次的实验很简单,下一个实验是 "进阶版"分频器,继续学习去了~

最后

以上就是火星上自行车最近收集整理的关于从零开始的FPGA学习6-加法/减法计数器加法计数器减法计数器结束语的全部内容,更多相关从零开始内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复