题目来源:牛客VL26

请编写一个序列检测模块,检测输入信号a是否满足011XXX110序列(长度为9位数据,前三位是011,后三位是110,中间三位不做要求),当信号满足该序列,给出指示信号match。

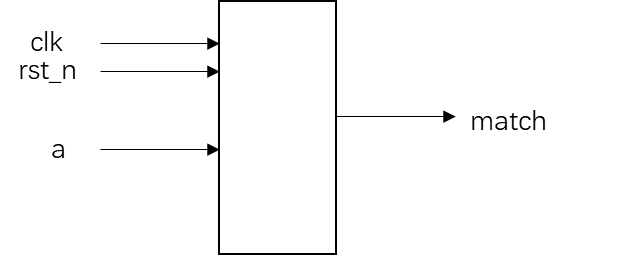

程序的接口信号图如下:

序列检测常用的两种方法,一种就是状态机(FSM) 另一种是 移位寄存器 ,由于本题序列较多,而且默认是重复序列检测,因此考虑到重复性,需要对X进行分类讨论(有可能存在含X构成的重复序列),这样的状态机会异常复杂,而使用移位寄存器的方法,会简单许多。

序列检测常用的两种方法,一种就是状态机(FSM) 另一种是 移位寄存器 ,由于本题序列较多,而且默认是重复序列检测,因此考虑到重复性,需要对X进行分类讨论(有可能存在含X构成的重复序列),这样的状态机会异常复杂,而使用移位寄存器的方法,会简单许多。

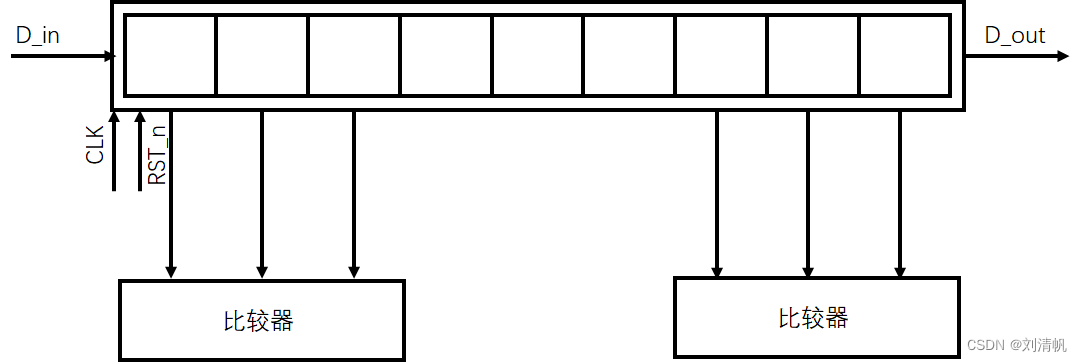

而移位寄存器,是一种类似于数据结构中的队列,有着 先入先出(FIFO) 的关系。本题需要检测的序列总共9位,因此将移位寄存器设置为9位,clk触发,rst_n复位的同步电路。其框图如下。

数据以数据流的形式随着时钟的上升沿进入/移出移位寄存器。寄存器中存入的数据就表示当前连续9bit的内容,将对应位与需要检测的数据进行比较,如果满足要求则输出检测到序列的标志。

数据以数据流的形式随着时钟的上升沿进入/移出移位寄存器。寄存器中存入的数据就表示当前连续9bit的内容,将对应位与需要检测的数据进行比较,如果满足要求则输出检测到序列的标志。

实现代码如下

`timescale 1ns/1ns

module sequence_detect(

input clk,

input rst_n,

input a,

output reg match

);

reg [8:0] buff_s;

always @(posedge clk or negedge rst_n) begin

if(~rst_n)

buff_s<=9'b0_0000_0000;//清除队列

else

buff_s<={a,buff_s[8:1]};//寄存器移位

end

always@(posedge clk or negedge rst_n)begin//比较器部分

if(~rst_n)

match<=0;

else

begin

if((buff_s[8:6]==3'b011)&&(buff_s[2:0]==3'b110))//if语句用于屏蔽x输入类型

match<=1;

else

match<=0;

end

end

endmodule

不重叠序列检测的情况

题目来源:牛客VL27

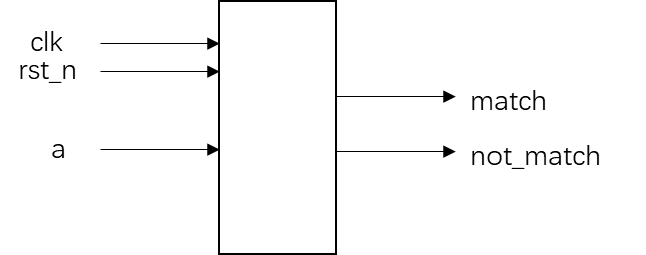

请编写一个序列检测模块,检测输入信号(a)是否满足011100序列, 要求以每六个输入为一组,不检测重复序列,例如第一位数据不符合,则不考虑后五位。一直到第七位数据即下一组信号的第一位开始检测。当信号满足该序列,给出指示信号match。当不满足时给出指示信号not_match

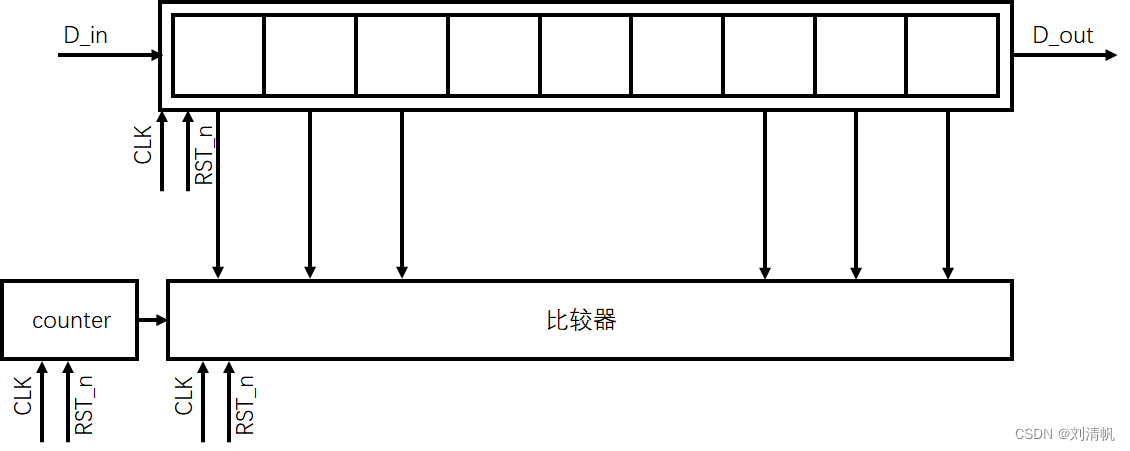

不重叠序列检测的核心就是定时检测,将序列划分成一组一组。例如对于9位的移位寄存器,可以设置一个检测计数器,每次计数到9时,表明上一组数据已经全部移出移位寄存器,可以进行一次新的数据比较器的检测操作。框图如下

实现代码如下

实现代码如下

`timescale 1ns/1ns

module sequence_detect(

input clk,

input rst_n,

input data,

output reg match,

output reg not_match

);

reg [5:0] shift_reg;

reg [2:0] count;

always @(posedge clk or negedge rst_n) begin

if(~rst_n)

shift_reg<=6'b00_0000;//清空队列

else

shift_reg<={data,shift_reg[5:1]};//移位

end

//计数模块

always @(posedge clk or negedge rst_n) begin

if(~rst_n)

count<=3'b0;

else

if(count==3'b101)

count<=3'b0;

else

count<=count+1;

end

always @(posedge clk or negedge rst_n) begin

if(~rst_n)

begin

match<=0;

not_match<=0;

end

else

begin

if(count==3'b101)

if(shift_reg==6'b011100)

begin

match<=1;

not_match<=0;

end

else

begin

match<=0;

not_match<=1;

end

else

begin

match<=0;

not_match<=0;

end

end

end

endmodule

最后

以上就是光亮爆米花最近收集整理的关于verilog移位寄存器实现序列检测的全部内容,更多相关verilog移位寄存器实现序列检测内容请搜索靠谱客的其他文章。

发表评论 取消回复