FPGA复位信号的设计处理

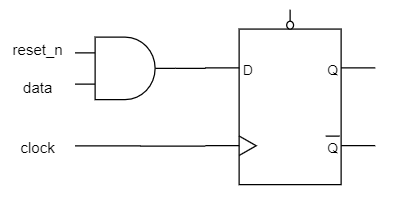

同步复位

同步复位:同步复位信号跟触发器的时钟是同步的,只有在时钟的跳变沿到来之后才会生效,对应verilog代码如下(这种写法会被编译器综合成同步复位):

always@(posedge clk) begin

if(!rst_n) begin

...

end

优点:可确保电路百分之百地为同步电路,所以同步复位的时序很容易被静态时序分析器分析。

缺点:大大增加资源消耗,触发器的输入端会增加一个LUT,同时也降低了系统能运行的最高时钟速度。

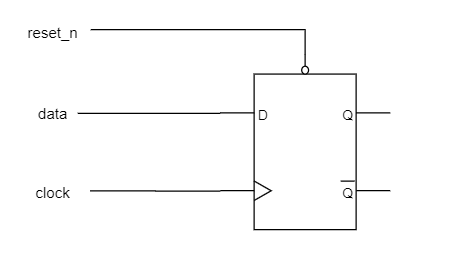

异步复位

异步复位:异步复位信号是直接到达寄存器的复位端,跟寄存器的时钟无确定的时序关系,对应的verilog代码如下(这种写法会被编译器综合成异步复位):

always@(posedge clk or negedge rst_n) begin

if(!rst_n) begin

...

end

优点:消耗资源少;不像同步复位那样需要插入到数据路径中,因此不会影响数据到达触发器的时间,可提高运行时钟;复位即刻生效,不像同步复位那样依赖于时钟。

缺点:异步复位是自然的到达触发器的复位端,与触发器所在时钟域无确定的时序关系,所以异步复位信号的时序分析比较困难;易受毛刺影响;在复位的时候,电路不会有什么问题,但是复位释放时,很容易产生亚稳态,且无法保证电路中各个触发器的异步复位与时钟之间的时序关系是一样的,就会导致有些触发器复位及时而其他的触发器在下一个时钟才会复位,这对于一个寄存器的下一个输出依赖于其他寄存器输出的反馈电路会致命性的影响。

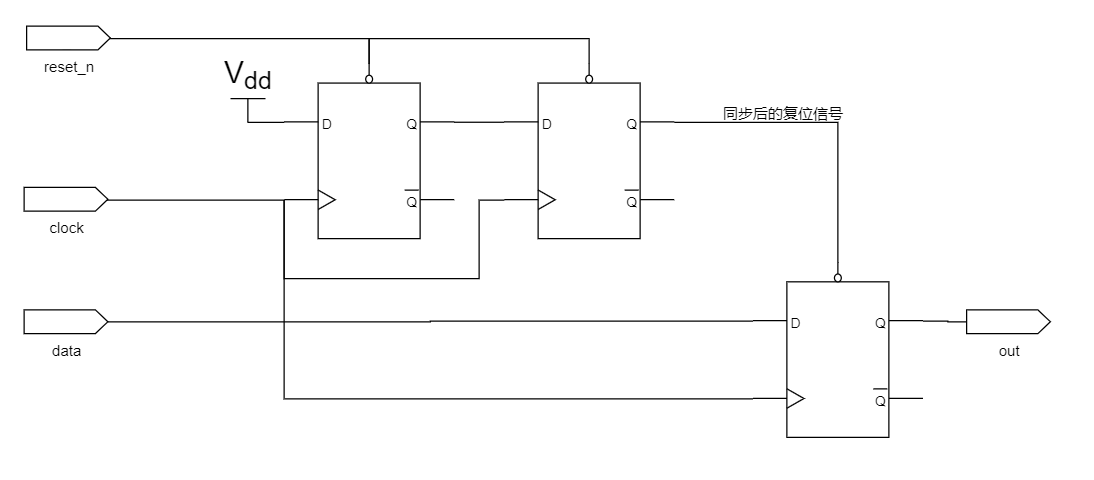

异步复位同步释放(推荐)

这种复位电路完美继承了同步复位和异步复位的优点且有效避免了这两者的缺点。对应的verilog代码如下:

module sync_async_reset(

input wire clock,

input wire reset_n,

input wire data_in,

output reg data_out

);

reg rstn_1,rstn_2;

always @(posedge clock or negedge reset_n) begin

if(!reset_n) begin

rstn_1<=1'b0;

rstn_2<=1'b0;

end else begin

rstn_1<=1'b1;

rstn_2<=rstn_1;

end

end

always @(posedge clock ) begin

if(!rstn_2) begin

data_out<=1'b0;

end else begin

data_out<=data_in;

end

end

endmodule

上面这种同步化的异步复位方式,可以做到即刻复位同步释放,但是容易受到噪声和窄脉冲干扰,故而最好对进入到FPGA的异步复位信号先进行滤波和去抖动。

友善提醒

不管是实现哪一种复位方式,虽然看起来没有增加什么代码量,但是他们消耗的FPGA资源远比你想象中要多得多,尤其是同步复位方式,复位的寄存器位宽越大消耗的资源就越多。因此,在设计的时候需要多想一步,这个复位是否真的有必要。典型的类似axi stream总线,一般情况下复位的时候只需要复位tready和tvalid即可。

最后

以上就是眯眯眼康乃馨最近收集整理的关于FPGA同步复位和异步复位的区别以及设计处理FPGA复位信号的设计处理的全部内容,更多相关FPGA同步复位和异步复位内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复