EDA技术题库

目录

EDA技术题库

一.填空题

二. 简述题

三、 选择题

四、 计算题(更全的,就看实验5678)

一.填空题

1. Verilog的基本设计单元是模块。它是由两部分组成,一部分描述接口;另一部分描述逻辑功能,即定义输入是如何影响输出的。

- 用assign描述的语句我们一般称之为组合逻辑,并且它们是属于并行语句,即于语句的书写次序无关。而用always描述的语句我们一般称之为组合逻辑或时序逻辑,并且它们是属于串行语句,即于语句的书写有关。

- 在case语句中至少要有一条default语句。

- 已知x=4’b1001,y=4’0110,则x的4位补码为4’b1111,而y的4位的补码为4’b0110 。

- 两个进程之间是并行语句。而在Always中的语句则是顺序语句。

- 综合是将高层次上描述的电子系统转换为低层次上描述的电子系统,以便于系统的具体硬件实现 。综合器是能自动将高层次的表述(系统级、行为级)转化为低层次的表述(门级、结构级)的计算机程序。

- 设计输入的方式有原理图、硬件描述语言、状态图以及波形图。

- IP核是知识产权核或知识产权模块,在EDA技术中具有十分重要的地位。半导体产业的IP定义为用于ASIC或FPGA中的预先设计好的电路功能模块。IP分为软IP、固IP和硬IP。

- Verilog中常用有两种变量:寄存器型变量(用reg定义)、网线型变量(用wire定义)。

- 两种可编程逻辑结构是基于与-或阵列可编程结构(乘积项逻辑可编程结构)、基于SRAM查找表的可编程逻辑结构。

- Verilog的端口模式有三种:输入端口、输出端口、双向端口,对应的端口定义关键词分别是:input、output、inout。

- Verilog中常用有两种变量:寄存器型变量(用reg定义)、网线型变量(用wire定义) 。

- Verilog有两种赋值方式:阻塞式赋值(=)、非阻塞式赋值(<=) 。

- Verilog有四种循环语句:for语句、repeat语句、while语句、forever语句。

- Verilog的描述风格:RTL描述 、数据流描述、行为描述、结构描述。

- 从状态机的信号输出方式上分,有Mealy型和Moore型两种状态机;从状态机的描述结构上分,有单过程状态机和多过程状态机;从状态机表达方式上分,有符号化状态机和确定状态编码的状态机;从状态机编码方式上分,有顺序编码状态机、一位热码编码状态机或其他编码方式状态机。

- 四种简单逻辑器件:PROM中固定的与阵列,可编程或阵列;PLA是与阵列、或阵列都可编程;PAL中或阵列固定,与阵列可编程;GAL是或阵列、与阵列都可编程,输入部分增加了输出逻辑同单元(OLMC)。

- 某一纯组合电路输入为in1,in2和in3,输入出为out,则该电路描述中always的事件表达式应写为always@(in1,in2,in3 );若某一时序电路由时钟clk信号上升沿触发,同步高电平复位信号rst清零,该电路描述中always的事件表达是应该写为always @( posedge clk )。

if(a) out1<=int1;

else out1<=int2;

当a= 1;执行out1<=int1;

当a= 0;执行out1<=int2。

- 4’b1001<<2= 4’b0100,4’ b1001>>2= 4’b0010。

- 下面程序中语句5、6、7、11是并行执行,语句9、10是顺序执行:

1 module M(……);

2 input ……. ;

3 output ……;

4 reg a,b……;

5 always@(……..)

6 assign f=c&d;

7 always@(……..)

8 begin

9 a=…….;

10 b=…….;

end

11 mux mux1(out,in0,in1);

Endmodule

- 用EDA技术进行电子系统设计的目标是最终完成ASIC的设计与实现。

- 可编程器件分为CPLD和FPGA。

- 随着EDA技术的不断完善与成熟,自顶向下的设计方法更多的被应用于Verilog HDL设计当中。

- 目前国际上较大的PLD器件制造公司有ALtera和Xilinx公司。

- 完整的条件语句将产生组合电路,不完整的条件语句将产生时序电路。

- 阻塞性赋值符号为 = ,非阻塞性赋值符号为 <= 。

- 有限状态机分为Moore和Mealy两种类型。

- EDA缩写的含义为电子设计自动化(Electronic Design Automation)。

- 状态机常用状态编码有二进制、格雷码和独热码。

- Verilog HDL中任务可以调用其他任务和函数。

- 系统函数和任务函数的首字符标志为 $ ,预编译指令首字符标志为 # 。

- 可编程逻辑器件的优化过程主要是对速度和资源的处理过程。

- 大型数字逻辑电路设计采用的IP核有软IP、固IP和硬IP。

- 操作符有 9 种类型,其中三目操作符有 2 个操作符和 3 个操作数。

- 关键字全是 小写 ,标识符的首字符必须是 字母 或 下划线 。

- 数字A=5’b011?的?表示 z 。设B=5’b101x1,C=5’b01x11,则操作运算F=B+C的结果F= 5'bxxxxx 。

- Verilog HDL中保存字符串“Hello”需要 40 位。

- 声明reg [7:0]data[4:0]表示 5 个 8 位的存储单元。

module test(q,clk,crt);

output q;

reg q;

input clk,crt;

always @(posedge clk)

begin

if(crt==1)

q=~q;

end

Endmodule

- 数据流建模的主要语法结构是assign LHS_target = RHS_expression; 语句,采用 assign 关键字开始。

- 大型数字逻辑电路设计采用的IP核有 软IP、固IP和硬IP。

- 简述题

- 简述自顶向下的设计方法I

答:①从自然语言说明到HDL的系统行为描述;②从HDL的系统行为描述到RTL描述;③从RTL描述到逻辑门级描述;④从门级描述到最终可以物理布线实现的底层电路;(以上可以理解成是逐步综合的过程。)⑤后期设计还包括涉及硬件实现和测试。

- 简述 EDA的设计流程

答:①图形输入:a.原理图b.硬件描述语言c.状态图d.波形图;②HDL文本输入﹔③综合;④适配;功能仿真与时序仿真;⑥编程下载;⑦硬件测试

- 简述什么是元件例化

答:元件例化就是引入一种连接关系,将预先设计好的元件,与当前设计模块中的指定端口相连接,从而构成层次化的设计方式。元件例化可以是多层次的,一个调用了较低层次元件的设计模块,也可以被更高层次的设计模块调用,成为高层次设计模块中的一个元件。被例化的元件可以以不同的形式出现,可以是Verilog,设计文件,可以是FPGA元件库中的元件,或者是以别的硬件描述语言设计的元件,还可以是IP核。

- 简要说明仿真时阻塞赋值与非阻塞赋值的区别

非阻塞(non-blocking)赋值方式( b<= a):

b的值被赋成新值a的操作,并不是立刻完成的,而是在块结束时才完成;块内的多条赋值语句在块结束时同时赋值;硬件有对应的电路。

阻塞(blocking)赋值方式( b = a):

b 的值立刻被赋成新值a;完成该赋值语句后才能执行下一句的操作;硬件没有对应的电路,因而综合结果未知。阻塞赋值是在该语句结束是立即完成赋值操作;非阻塞赋值是在整个过程块结束是才完成赋值操作。

- 简述if语句的几种主要结构

答:①if(条件表达式)

begin 语句块; end

②if(条件表达式)

begin语句块1; end

else begin 语句块2; end

③if(条件表达式1)

begin 语句块1; end

else if(条件表达式2)begin语句块2;

end …

else if(条件表达式n)

begin 语句块n; end

else begin 语句块n+1; end

- 简述Moore型和Mealy型状态机的区别-

答:Mealy型状态机的输出是当前状态和所有输入信号的函数,它的输出是在输入变化后立即发生的,不依赖时钟的同步。Moore型状态机的输出则仅为当前状态的函数,这类状态机在输入发生变化时还必须等待时钟的到来,时钟状态发生变化时才导致输出的变化,所以比 Mealy机要多等待一个时钟周期。

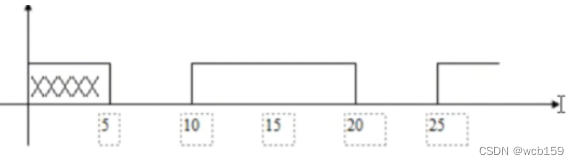

- 画出下面程序段中r(reg型)的仿真波形(6分)

fork

# 20 r=1’ b0 ;

# 10 r=1’ b1;

# 15 r=1’ b1;

# 25 r=1’ b1;

# 5 r=1’ b0;

Join

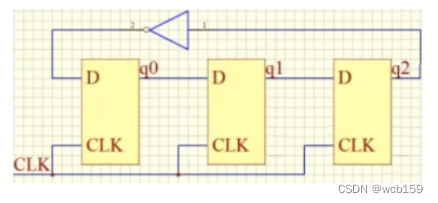

- 画出下面程序综合出来的电路图。(7分)

always@(posedge clk)

begin

q0<=~q2;

q1<= q0;

q2<= q1;

End

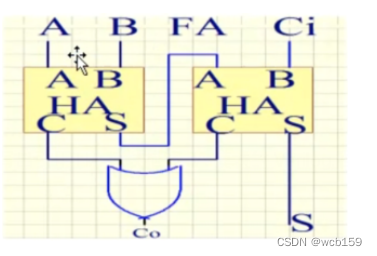

- HA模块程序如下,写出引用HA模块描述FA模块的Verilog,程序。(7分)

module HA(A,B,S,C) ;

inputA,B;

output S, C;

assign {C,S}=A+B;

endmodule

module FA(A,B,Ci,Co,S);

input A,B,Ci ;

output Co,S;

wire S1,C1,C2;

HA a(A,B,S1,C1);

HA b(S1,Ci,C2,S);

assign Co=C1 | C2 ;

endmodule

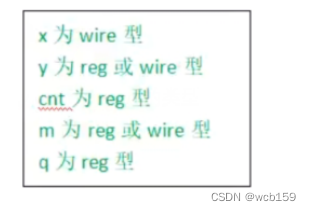

- 写出下面程序中变量x,y,cnt,m,q的类型

Assgin x=y ;

always@(posegde clk)

begin

cnt=m+1;

q=~q;

end

- 定义如下的变量和常趣:

(1)定义一个名为count 的整数;(integer count>

(2)定义一个名为ABUS的8位wire总线;(wire [7:0] ABUS)

(3)定义一个名为address 的16位reg型变量,并将该变量的值赋为十进制数128;(reg[15:0] address address = 16'd128)

(4)定义参数Delay_time,参数值为8;(parameter Delay_time = 8)

(5)定义一个名为 DELAY的时间变量;(没讲过)

(6)定义一个32位的寄存器MYREG;(reg [31:0] MYREG;)

(7)定义一个容量为128,字长为32位的存储器MYMEM,(reg [31:0] MYMEM [127:0])

- 下列标识符哪些是合法的,哪些是错误的?

Cout(y),8sum(n),a*b(y),data(y),wait(y), initial(n),$1atch(n)

答:

合法的:Cout(y),wait(y),initial(n),$1atch(n)

错误的:8sum(n),a*b(y),data(y)

- 下列数字的表示是否正确?

6'd18(y),'Bx0(y),5' b0x110(y),'da30(n),10’d2(y),'hzF(y)

答:

合法的:'Bx0(y),'da30(n),'hzF(y)

错误的:6'd18(y),5' b0x110(y),10’d2(y)

- 简述有限状态机FSM分为哪两类﹖有何区别?有限状态机的状态编码风格主要有哪三种?

答:根据内部结构不同可分为摩尔型状态机和米里型状态机两种。摩尔型状态机的输出只由当前状态决定,而次态由输入和现态共同决定;米里型状态机的输出由输入和现态共同决定,而次态也由输入和现态决定。

状态编码主要有三种:连续二进制编码、格雷码和独热码。

- 简述基于数字系统设计流程包括哪些步骤?

答:包括五个步骤:

(1)、设计输入:将设计的结构和功能通过原理图或硬件描述语言进行设计或编程,进行语法或逻辑检查,通过表示输入完成,否则反复检查直到无任何错误。

2)、逻辑综合:将较高层的设计描述自动转化为较低层次描述的过程,包括行为综合,逻辑综合和版图综合或结构综合,最后生成电路逻辑网表的过程。

(3、布局布线:将综合生成的电路网表映射到具体的目标器件中,并产生最终可下载文件的过程。

(4)、仿真:就是按照逻辑功能的算法和仿真库对设计进行模拟,以验证设计并排除错误的过程,包括功能仿真和时序仿真。

(5)、编程配置:将适配后生成的编程文件装入到PLD器件的过程,根据不同器件实现编程或配置。

- 程序注解,并说明整个程序完成的功能。

module AAA ( a ,b ); //定义模块名为AAA,端口为a,b

output a ; //定义a为输出端口

input [6:0] b; //定义b为输出端口,b为7为二进制数

reg[2:0] sum; //sum为reg型变量,用以统计赞同的人数

integer i; //定义整型变量,i为循环控制变量

reg a; //定义a为寄存器变量

always @(b) //过程语句,敏感变量为b

begin //语句块

sum= 0; //sum初始值为0

for(i = 0;i<=6;i = i+1) //for语句,统计b为1的个数

if(b[i]) //条件语句

sum=sum+1; //只要有人投赞成票,则sum加1

if(sum[2]) a=1; //若超过4人则表决通过

else a=0 //若不到4人则不通过

- 选择题

- 已知“a=1b’1;b=3b'001;”那么{a,b}= ( C )

(A) 4b'0011

(B) 3b'001

(C) 4b'1001

(D) 3b'101

- 在verilog.中,下列语句哪个不是分支语句? ( D )

(A) if-else

(B) case

(C) casez

(D) repeat

- 在verilog.语言中,a=4b'1011. 那么&a= (D )

(A) 4b'1011

(B) 4b1111

(C) 1b'1

(D) 1b'0

- 在verilog.语言中整型数据与(C )位寄存器数据在实际意义上是相同的。

(A) 8

- 16

- 32

- 64

- 大规模可编程器件主要有FPGA、CPLD 两类,下列对FPGA结构与工作原理的描述中正确的是(C)

A. FPGA全称为复杂可编程逻辑器件;

B. FPGA是基于乘积项结构的可编程逻辑器件;

C.基于SRAM的FPGA器件,在每次上电后必须进行-次配置;

D.在Altera公司生产的器件中,MAX7000 系列属FPGA结构。

- 子系统设计优化,主要考虑提高资源利用率减少功耗(即面积优化),以及提高运行速度(即速度优化);指出下列哪些方法是面积优化(B)

①流⽔线设计②资源共享③逻辑优化④串⾏化⑤寄存器配平⑥关键路径法

- ①③⑤

- ②③④

- ②⑤⑥

- ①④⑥

- 下列标识符中, A 是不合法的标识符。

A. 9moon

B. State0

C. Not_ Ack 0

D,signall

- 下列语句中,不属于并行语句的是:(D)

A. 过程语句

B. asgn语句

C. 元件例化语句

D. case 语句

- P,Q,R都是4bit的输入矢量, 下面哪一种表达形式是正确的 5)

1) input P[3:0],Q,R:

2) input P, Q,R[3:0];

3) input P[3:0], Q[3:0], R[3;0]:]

4) input [3:0] P, [3:0]Q, [0:3]R;

5) input [3:0] P,Q,R;

- 下列标示符哪些是合法的(B)

A、 Stime

B、 ._date

C、 8sum

D、 mux#

- 如果线网类型变量说明后未赋值,起缺省值是(D)

A、x

B、1

C、0

D、Z

- 现网中的值被解释为无符号数。在连续赋值语句中assign addr3:0];3;addr被赋与的值是(A)

A、4' b1101

B、4' b0011

C、4' bxox11

D、4' bzz11

- reg[7:0] memal255:0]正确的赋值是(A)

A、 mema151=3’do.

B、 8’d0:

- 1’b1:

- mema[51[3:01=4’d

- 在code模块中参数定义如下,请问top模块中d1模块delay1、 delay2 的值是(D)

module code(x,v);

module top;

paramee delay1= 1,delay2=1;

........

code #(1,5) d1(x1,V1);

endmodule

Endmodule

- (1,1)

- (5,5)

- (5,1)

- (1,5)

- "a=4' b11001,be4' bx110 "选出正确的运算结果(B)

- a&b=O

- a&&b=1

- b&a=x

- b&&a=x

- 时间尺度定义为timescale 10ns/100ps.选择正确答案( C)

- 时间精度10ns

- 时间单位100ps

- 时间精度100ps

- 时间精度不确定

- 若a=9,执行Sdisplay( “current value=%0b,a=%0d" ,a,a)正确显示为(B )

A、current value= 1001,a=09

B、current vale= 1001,a=9

C、1001,9

D、current vl00..10001,a=9

- aways begin #5 clk=0; #10 clk-~ck;end产生的波形(A)

A、 占空比1/3

B、 dk=1

C、 dk≈0

D、 周期为10

- 在Verilog.中定义了宏名'define sum atb+c下面宏名引用正确的是( A)

A、 out='sum+d;

B、 out-sum+d;

C、 out=' sum+d;

D、 都正确

- 下面哪个是可以用verilog语言进行描述,而不能用VHDL语言进行描述的级别? (A )

(A) 开关级

(B) 门电路级

(C) 体系结构级

(D) 寄存器传输级

- 在verilog.中,下列语句哪个不是分支语句? ( D )

(A) if-else

(B) case

(C) casez

(D) repeat

- 下列哪些Verilog的基本门级元件是多输出(D)

(A) nand

(B) nor

(C) and

(D) not

- Verilog 连线类型的驱动强度说明被省略时,则默认的输出驱动强度为(B )

(A) supply

(B) strong

(C) pull

(D) weak

- 元件实例语句“noti1 #(1:34,2:3:4,1:2:4) Ulout,in,ctrD;"中截至延迟的典型值为(B )

(A)1

(B)2

(C)3

(D)4

- 已知“a=1b' 1; b=3b'001;"那么{a,b}= ( C)

(A) 4b"0011

(B) 3b'001

(C) 4b'1001

(D) 3b'101

- 根据调用子模块的不同抽象级别,模块的结构描述可以分为(ABC )

(A) 模块级

(B) 门级

(C) 开关级

(D) 寄存器级

- 在verilog语言中, a=4b'1011. 那么&a= ( D)

(A) 4b'1011

(B) 4)1111

(C) 1b'1

(D) 1b'0

- 在verilog,语言中整型数据与(C)位寄存器数据在实际意义上是相同的。

(A) 8

(B) 16

- 32

- 64

- 状态机编码方式中,其中 A 占用触发 器较多,但其简单的编码方式可减少状态译码组合逻辑资源,且易于控制非法状态。

A. 一位热码编码

B. 顺序编码

C 状态位直接输出型编码

- 格雷码编码

- 综合是EDA设计流程的关键步骤。在下面对综合的描述中,

错误的是(D)

A.综合就是把抽象设计层次中的一.种表示转化成另--种表示的过程。

B.综合就是将电路的高级语言转化成低级的,可与FPGA/ CPLD的基本结构相映射的网表文件。

C.为实现系统的速度、面积、性能的要求,需要对综合加以约束,称为综合约束。

D.综合可理解为,将软件描述与给定的硬件结构用电路网表文件表示的映射过程,并且这种映射关系是唯-的(即综合结果是唯-的)。

- 规模可编程器件主要有FPGA. CPLD两类,其中CPLD通过_ A_ 实现其逻辑功能。

A.可编程乘积项逻辑

B.查找表(LUT)

C.输入缓冲

D.输出缓冲

- 不完整的IF语句,其综合结果可实现(A) 。

A.时序逻辑电路

B.组合逻辑电路

C.双向电路

D.三态控制电路

- 基于EDA软件的FPGA/CPLD设计流程为:原理图/HDL文本输入→(A) →综合→适配一____ 一编程下载一硬件测试。

A.功能仿真

B.时序仿真

C.逻辑综合

D.配置

- IP核在EDA技术和开发中具有十分重要的地位:提供用VHDL等硬件描述语言描述的功能块,但不涉及实现该功能块的具体电路的IP核为(A) 。

A.软IP

B.固IP

C.硬IP

D.全对

- 计算题(更全的,就看实验5678)

(1)2/4分频器Verilog描述语句

module div_2_4(reset,clk_in,clk2_out,clk4_out);

input clk_in,reset;

output clk2_out,clk4_out;

reg clk2_out,clk4_out;

always @(posedge clk_in) //时钟上升沿触发

begin

if(~reset)begin //同步复位

clk2_out<=0;

clk4_out<=0;

end

else begin

clk2_out<= ~clk2_out ;

if(~ clk2_out) clk4_out<= ~clk4_out ;

end

end

Endmodule

(2)1/6,10分频参考程序(N=6,10)

module div_6(reset,clk_in,clk6_out,clk10_out);

input clk_in,reset;

output clk6_out,clk10_out;

reg clk6_out,clk10_out;

parameter WIDTH=3;

reg [WIDTH:0]temp1,[WIDTH:0]temp2;

always @(posedge clk_in)

begin

if(~reset)begin

clk6_out<=0;

clk10_out<=0;

temp1<=2;temp2<=4; end //使复位后的第一个时钟

else begin //就开始分频

temp1= temp1+1 ; temp2= temp2+1;

if(temp1>2) begin clk6_out<= ~clk6_out ;

temp1<=0; end

if(temp2>4) begin clk10_out<= ~clk10_out ;

temp2<=0; end

end

end

endmodule

- 占空比为50%的三分频器Verilog描述程序

module fen3(clkin,qout1,qout2,clkout);

input clkin;

output reg qout1,qout2;

output clkout; wire clkout;

assign clkout=qout1|qout2;

always @(posedge clkin)

begin : blk1

reg[1:0] cnt;

if(clkin==1'b1)begin

if(cnt<1)begin

qout1<=1'b1;

cnt<=cnt+1;end

else begin

qout1<=1'b0;

cnt<=cnt+1;

if(cnt>1) cnt<=0;end

end

end

always @(negedge clkin)

begin : blk2

reg[1:0] cnt;

if(clkin==1'b0)begin

if(cnt<1)begin

qout2<=1'b1;

cnt<=cnt+1;end

else begin

qout2<=1'b0;

cnt<=cnt+1;

if(cnt>1) cnt<=0;end

end

end

endmodule

(4)由输入信号检测010序列Verilong程序

module mealyfsm(clk,reset,din,dout, cs_state,ns_state);

output dout;

output [1:0] cs_state,ns_state;

input clk,reset,din;

reg dout;

//用格雷码编码声明状态值

parameter [1:0] s0=2'b00,s1=2'b01,s2=2'b11;

reg [1:0]cs,ns;

assign cs_state=cs,ns_state=ns;

always@(posedge clk,posedge reset)begin

if(reset==1'b1) //异步复位,高电平有效

cs<=s0;

else

cs<=ns; end

//次态计算及输出信号产生,

always@(cs,din)

case(cs)

s0:begin

dout=1'b0;

if(din===1'bx)ns=s0;

else ns=(din)?s0:s1;

end

s1:begin

dout=1'b0;

ns=(!din)?s1:s2;

end

s2:begin

dout=(din)?1'b0:1'b1;

ns=(din)?s0:s1;

end

default:begin

dout=1'b0;

ns=s0;

end

endcase

endmodule

(5)BCD码编码器程序:采用行为描述实现编码逻辑电路功能

module BCD_Enc(in,out);

input[9:0] in;

output[3:0] out; reg[3:0]out;

always @(in) //always过程语句

begin

case(in)

10‘b00_0000_0001:out=0;

10‘b00_0000_0010:out=1;

10‘b00_0000_0100:out=2;

10‘b00_0000_1000:out=3;

10‘b00_0001_0000:out=4;

10‘b00_0010_0000:out=5;

10‘b00_0100_0000:out=6;

10‘b00_1000_0000:out=7;

10‘b01_0000_0000:out=8;

10‘b10_0000_0000:out=9;

endcase

end

Endmodule

- BCD码函数调用

module bcd_enc(in,out);

input[9:0]in; output[3:0]out;

assign out=func_enc(in); //函数调用

function [3:0] func_enc; //函数定义

input[9:0] in;

case(in)

10'b00_0000_0001:func_enc=0;

10'b00_0000_0010:func_enc=1;

10'b00_0000_0100:func_enc=2;

10'b00_0000_1000:func_enc=3;

10'b00_0001_0000:func_enc=4;

10'b00_0010_0000:func_enc=5;

10'b00_0100_0000:func_enc=6;

10'b00_1000_0000:func_enc=7;

10'b01_0000_0000:func_enc=8;

10'b10_0000_0000:func_enc=9;

endcase

endfunction

endmodule

最后

以上就是俊秀小虾米最近收集整理的关于EDA技术题库EDA技术题库的全部内容,更多相关EDA技术题库EDA技术题库内容请搜索靠谱客的其他文章。

发表评论 取消回复