目录

1、同步复位

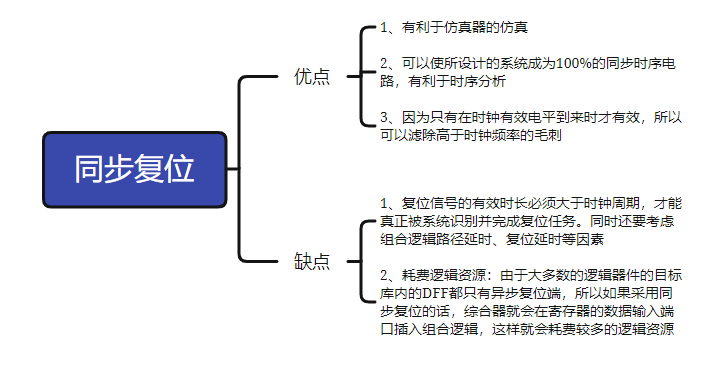

同步复位的优缺点:

2、异步复位

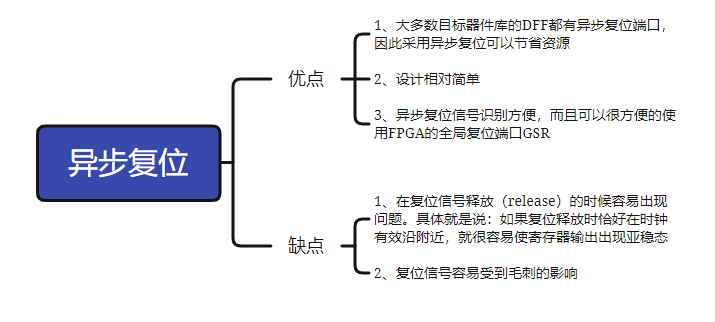

异步复位的优缺点:

3、异步复位同步释放

1、同步复位

同步复位,即如果复位信号有效,则只能在时钟上升沿让电路复位。

always @ (posedge clk) begin

if (!rst_n)

xxxx;

end

注意:在此always块中,敏感量只有一个,即clk的上升沿,此含义是,只有在clk的上升沿才能执行always块,否则不执行。于是如果复位信号有效,也只能等到clk上升沿才能执行always块,才能使电路复位!

同步复位的优缺点:

2、异步复位

复位信号不受时钟的控制,无论时钟沿是否到来,只要复位信号有效,就会对系统进行复位。

一般让复位信号低电平有效。

always @ (posedge clk or negedge rst_n)

begin

if (!rst_n)

xxxx;

else if (xx)

begin

xxxx;

end

end

注意:在此always块中,敏感量为两个,一个是clk的上升沿(posedge clk),一个是复位信号rst_n的下降沿(negedge rst_n),当复位信号下降沿出现时,不论clk在什么状态,都执行always块,即复位!

异步复位的优缺点:

3、异步复位同步释放

假设复位信号低电平有效rst_n,当复位信号无效时,也就是复位信号拉高时,即为复位信号的释放。

由于异步复位信号与时钟无必然联系,两者都是独立的,所以复位信号的释放将有一定的概率导致电路出现亚稳态。

所谓异步复位同步释放,就是在rst_n信号为低时,立刻进行复位,而rst_n信号由低到高释放时,为了防止亚稳态的出现,将rst_n信号用DFF向后延一周期,达到与时钟clk边沿同步的目的。

经典的异步复位同步释放代码如下:

module asyn_reset(

clk ,

rst_n ,

rst_s2

);

input clk ;

input rst_n ;

output reg rst_s2;

reg rst_s1;

always @ (posedge clk or negedge rst_n) begin

if (!rst_n) begin

rst_s1 <= 1'b0;

rst_s2 <= 1'b0;

end

else begin

rst_s1 <= 1'b1 ;

rst_s2 <= rst_s1 ;

end

end

endmodule

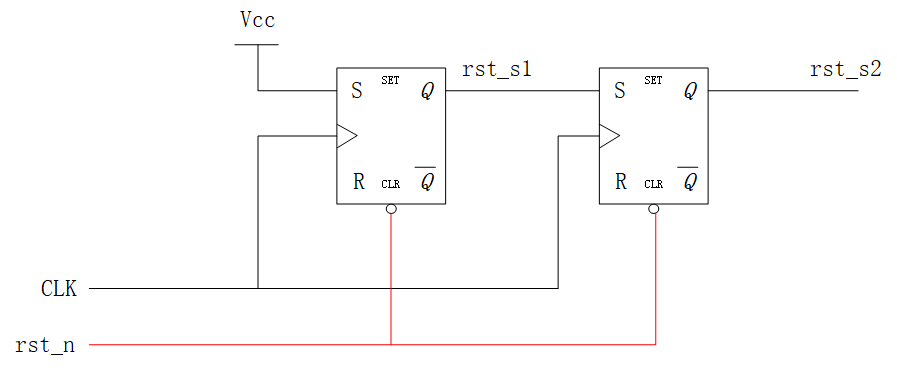

综合出的电路如下:

复位信号拉高,相当于rst_n对高电平进行采样;

由于异步复位需要在时钟上升沿进行释放,故在rst_n=1后,让信号rst_s1对电平1进行采样,之后再打一拍到寄存器rst_s2。相当于高电平被打了两拍才输出到rst_s2,达到了复位信号的释放与时钟clk同步的目的。

参考文献:

https://blog.csdn.net/qq_15062763/article/details/90904439

https://wenku.baidu.com/view/c37de13833687e21af45a9b4.html?fixfr=jKwnv4c1UWtlWAAJ3HoeFA%253D%253D&fr=income3-wk_app_search_ctr-search

https://wenku.baidu.com/view/2e6e9cfa941ea76e58fa049c.html?fixfr=QTAlS%252BuwrTmm0T%252BOwLb2pw%253D%253D&fr=income1-wk_app_search_ctr-search

最后

以上就是俊逸画板最近收集整理的关于同步复位、异步复位、异步复位同步释放的全部内容,更多相关同步复位、异步复位、异步复位同步释放内容请搜索靠谱客的其他文章。

发表评论 取消回复