使用Verilog语言生成7位伪随机码

代码

移位寄存器初始状态设为111_1111

本原多项式F(x)=x5+x2+1

工程文件:

module code(clk,rst,ena,m_out,data_out,load);

input clk; //时钟信号

input rst; //复位信号,低电平有效

input ena; //控制信号,高电平时序列发生器开始工作

output m_out; //数据信号,输出为m伪随机序列

output data_out;

output load; //控制信号,为高电平时表示伪随机序列开始

reg m_out,data_out,load;

reg [4:0]shift; //5级移位寄存器产生周期为31的序列

reg [6:0]temp; //7级移位寄存器产生周期为127的m序列

always @(posedge clk) begin

if(!rst) //初始化

begin

m_out <= 1'b0; //将数据信号置零

data_out <= 1'b0;

load <= 1'b0; //控制信号设为无效

shift <= 5'b1111_1; //移位寄存器初始状态设为全1

temp <= 7'b1111_111; //移位寄存器初始状态设为全1

end

else begin //开始产生序列信号

if(ena) //判断序列发生器的控制信号是否有效

begin //若控制信号有效

load <= 1'b1; //将控制伪随机序列产生的信号设为有效

shift <= {shift[3:0],shift[0]}; //移位

m_out <= shift[4]; //将移位寄存器的最高位做为m序列进行输出

shift[0] <= (shift[1]^shift[4]); //0位的值等于1位与4位相异或,对应本原多项式F(x)=x^5+x^2+1

temp <= {temp[5:0],temp[0]}; //移位

data_out <= temp[6]; //将移位寄存器的最高位做为m序列进行输出

temp[0] <= (temp[2]^temp[6]); //对应f(x)=x^7+x^3+1

if(load) //当控制伪随机数列产生的信号使能时

m_out <= shift[4]; //将移位寄存器的最高位做为m序列进行输出

data_out <= temp[6]; //将移位寄存器的最高位做为m序列进行输出

end

else load <= 1'b0; //若控制信号无效,则不开始产生伪随机序列

end

end

endmodule

仿真程序:

`timescale 1ns/1ns

module code_tb;

reg clk; //定义激励信号

reg rst;

reg ena;

wire m_out; //定义待测信号

wire data_out;

wire load;

code code_0(.clk(clk), //例化待测试模块

.rst(rst),

.ena(ena),

.m_out(m_out),

.data_out(data_out),

.load(load));

always #25 clk = ~clk; //产生20Mbp速率的码字

initial begin //定义输入信号的状态

clk = 0;

rst = 0;

ena = 0;

#40 rst = 1'b1;

#50 ena = 1'b1;

#20_000;

$stop;

end

endmodule

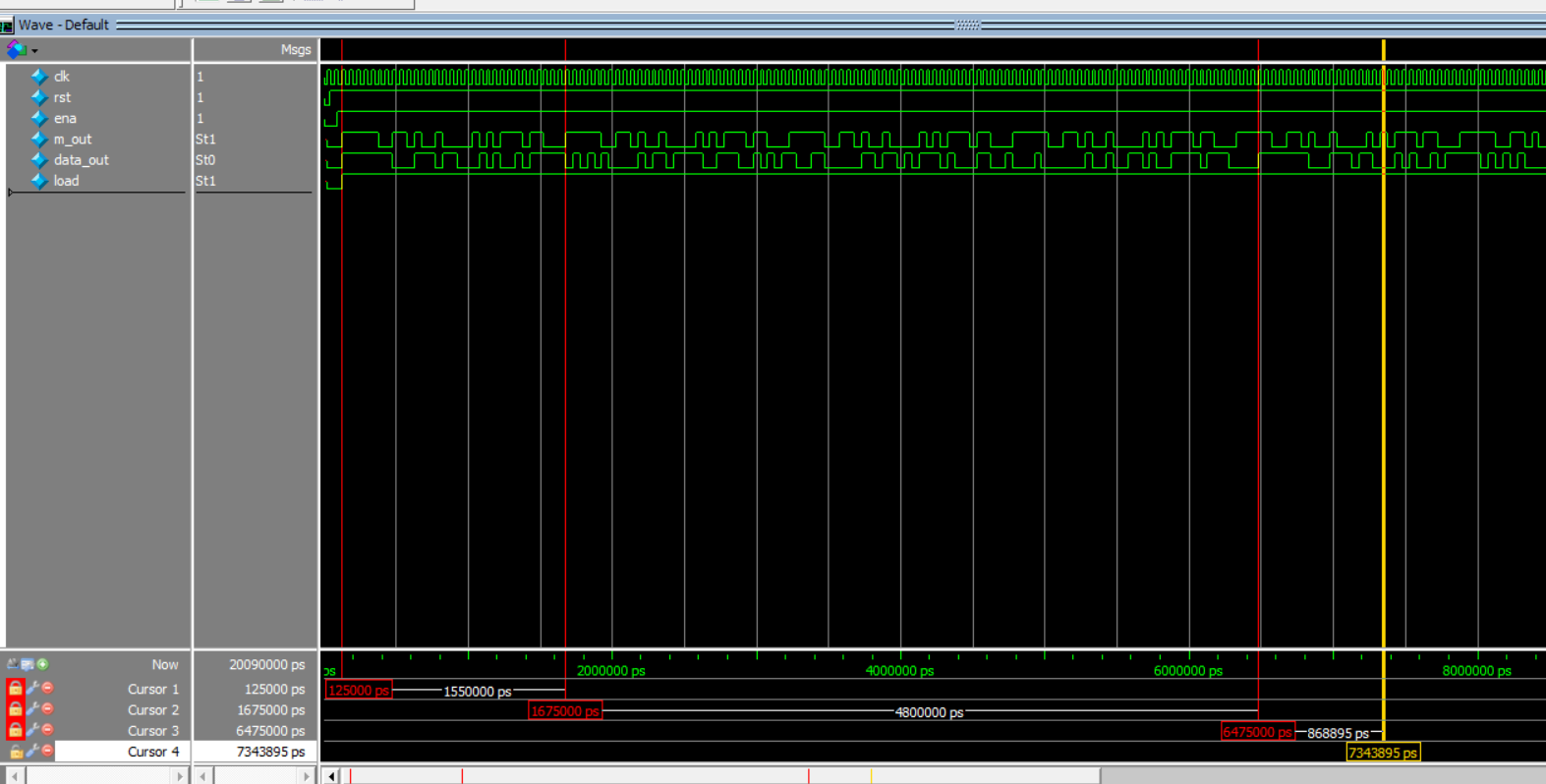

仿真效果

最后

以上就是糟糕含羞草最近收集整理的关于使用Verilog语言生成7位伪随机码的全部内容,更多相关使用Verilog语言生成7位伪随机码内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复