我是

靠谱客的博主

故意麦片,这篇文章主要介绍

Gray Counter (格雷码计数器),现在分享给大家,希望可以做个参考。

异步FIFO采用Gray Counter产生读写地址,Empty/Full信号的产生也与Gray Counter的最高两位相关。

| `timescale 1ns / 1ps

//

// Company: SEU.IC

// Engineer: Ray

//

// Create Date: 21:58:22 03/28/2011

// Design Name: Gray Counter

// Module Name: GrayCounter

// Revision 0.01 - File Created

//

module GrayCounter(

Clock,

Reset_in,

Enable_in,

GrayCount_out

);

parameter COUNTER_WIDTH = 5;

input Clock;

input Reset_in;

input Enable_in;

output [COUNTER_WIDTH - 1 : 0]GrayCount_out;

reg [COUNTER_WIDTH - 1 : 0] BinaryCount;

wire [COUNTER_WIDTH - 1 : 0]GrayCount_out;

always @(posedge Clock or negedge Reset_in)

begin

if(!Reset_in)

BinaryCount <= 'd0;

else if (Enable_in)

BinaryCount <= BinaryCount + 'd1;

end

assign GrayCount_out = {BinaryCount[COUNTER_WIDTH-1],

BinaryCount[COUNTER_WIDTH-1 : 1] ^ BinaryCount[COUNTER_WIDTH-2 : 0]};

endmodule

|

对应的testbench如下所示,

| `timescale 1ns / 1ps

// Company: SEU.IC

// Engineer:Ray

//

// Create Date: 22:18:38 03/28/2011

// Design Name: GrayCounter

// Module Name: E:/ray_study_verilog/Asynchronous_FIFO/tb_gray.v

// Project Name: Asynchronous_FIFO

// Target Device:

// Tool versions:

// Description:

//

// Verilog Test Fixture created by ISE for module: GrayCounter

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

module tb_gray; // Inputs

reg Clock;

reg Reset_in;

reg Enable_in; // Outputs

wire [4:0] GrayCount_out; // Instantiate the Unit Under Test (UUT)

GrayCounter uut (

.Clock(Clock),

.Reset_in(Reset_in),

.Enable_in(Enable_in),

.GrayCount_out(GrayCount_out)

); always #20 Clock = ~Clock;

initial begin

// Initialize Inputs

Clock = 0;

Reset_in = 0;

Enable_in = 0; // Wait 100 ns for global reset to finish

#100;

Reset_in = 1;

// Add stimulus here

#100

Enable_in = 1;

end

endmodule |

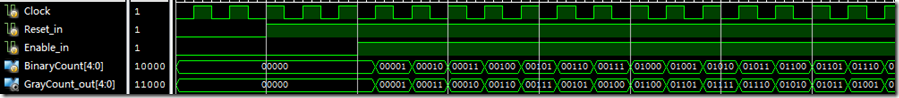

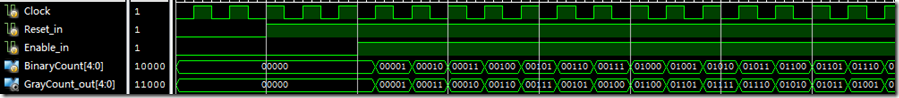

Xilinx ISE ISIM的仿真波形为:

最后

以上就是故意麦片最近收集整理的关于Gray Counter (格雷码计数器)的全部内容,更多相关Gray内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复