数字电路基础知识(三) 复位设计-异步复位,同步释放

一、基本电路原理

同步电路中的亚稳态完全可以避免。异步电路中的亚稳态无法回避,只能力求将影响降到可容忍的范围内。

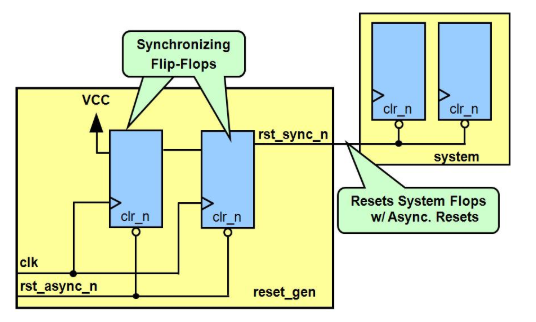

所以基于之前基于亚稳态采用异步置位同步释放的实现如下(网络图片,侵删)

下面分析此电路如何实现异步复位和同步释放的。

异步复位:显而易见,rst_async_n异步复位后,rst_sync_n将拉低,即实现异步复位。

同步释放:这个是关键,看如何实现同步释放,即当复位信号rst_async_n撤除时,由于双缓冲电路的作用,rst_sync_n复位信号不会随着rst_async_n的撤除而撤除。

假设rst_async_n撤除时发生在clk上升沿,如果不加此电路则可能发生亚稳态事件。但是加上此电路以后,假设第一级D触发器clk上升沿时rst_async_n正好撤除,则D1触发器输出高电平“1”,此时第二级触发器也会更新输出,但是输出值为前一级触发器次clk来之前时的Q1输出状态。显然Q1之前为低电平,顾第二级触发器输出保持复位低电平,直到下一个clk来之后,才随着变为高电平。即同步释放。

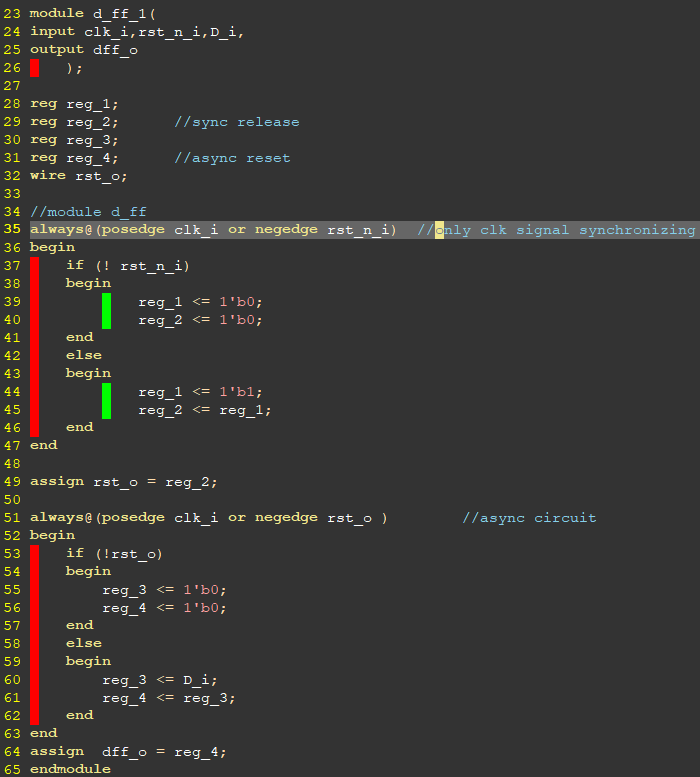

二、vivado用verilog实现

- verilog实现:

//Asynchronous reset, synchronous release

module d_ff_syncro(

input clk_i,rst_n_i,

output rst_o);

reg reg_1;

reg reg_2;

//module d_ff

always@(posedge clk_i or negedge rst_n_i) //only clk signal synchronizing

begin

if (! rst_n_i)

begin

reg_1 <= 1'b0;

reg_2 <= 1'b0;

end

else

begin

reg_1 <= 1'b1; //high level, two dff

reg_2 <= reg_1;

end

end

assign rst_o = reg_2;

endmodule

-

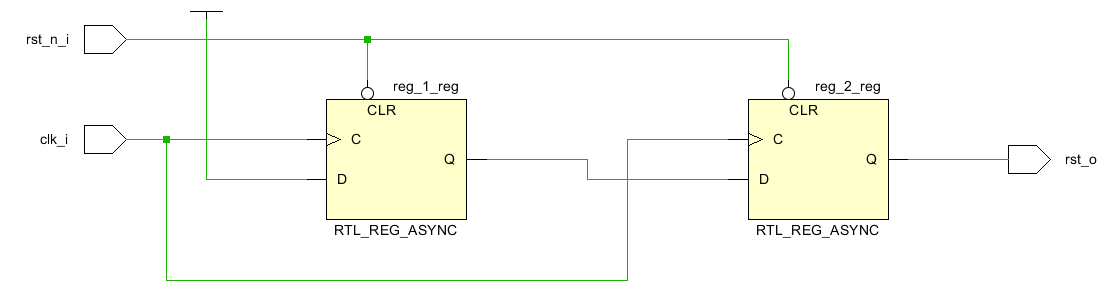

RTL电路实现如下:

-

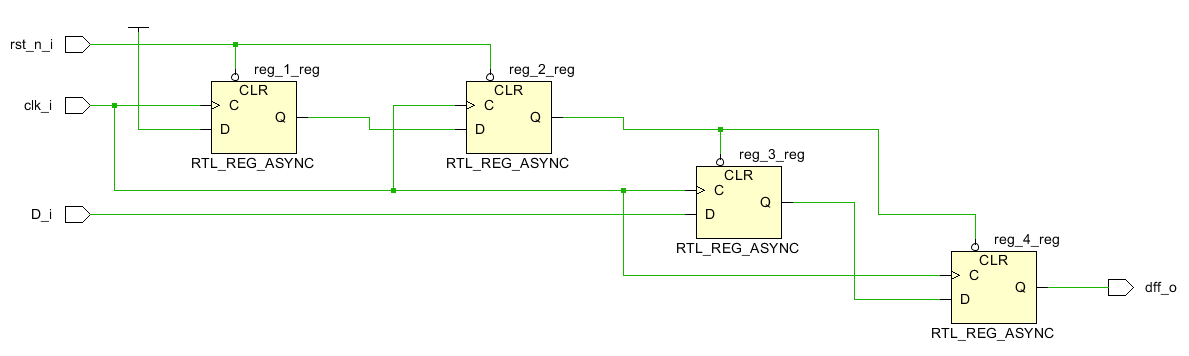

在异步复位中的同步释放电路

-

RTL电路实现简单的电路

利用前面两级触发器实现。需要注意的地方有如下几点:

1.第一级触发器的数据端口是接电源,即高电平1’b1。

2.第一级触发器的输出,不能使用,因为仍存在亚稳态的危险。两级触发器做同步,是非总线信号的最常见异步处理方法。总线信号的异步处理方法,常见的是异步FIFO实现。第一级触发器的输出,永远存在亚稳态的可能。 当第一级触发器采样异步输入之后,允许输出出现的亚稳态可以长达一个周期,在这个周期内,亚稳态特性减弱。在第二个时钟沿到来时,第二级同步器采样,之后才把该信号传递到内部逻辑中去。第二级输出是稳定且已被同步了的。如果在第二级采样时保持时间不够,第一级的输出仍然处于很强的亚稳态,将会导致第二级同步器也进入亚稳态,但这种故障出现的概率比较小。

3. 采用两级的触发器设计并不能完全消除亚稳态,知识大大降低出现亚稳态的概率,通常来说,两级的触发器设计能够满足设计的要求。

参考博文:https://blog.csdn.net/dongdongnihao_/article/details/79827076

最后

以上就是有魅力雪糕最近收集整理的关于数字电路基础知识(三) 复位设计-异步复位,同步释放的全部内容,更多相关数字电路基础知识(三)内容请搜索靠谱客的其他文章。

发表评论 取消回复