计数器IP核调用

- 计数器IP核使用

- FPGA设计方式

- 计数器IP核配置

- Ip核实现到硬件RTL结构

- 功能仿真

- IP核调用实现计数器级联

计数器IP核使用

FPGA设计方式

1、原理图输入(不推荐)系统比较大的时候修改十分困难

2、Verilog HDL设计方式

3、IP核输入方式(例如FFT的实现,包括的原理到最终实现,使用verilogHDL进行开发内容多开发周期太长,缩短开发周期)

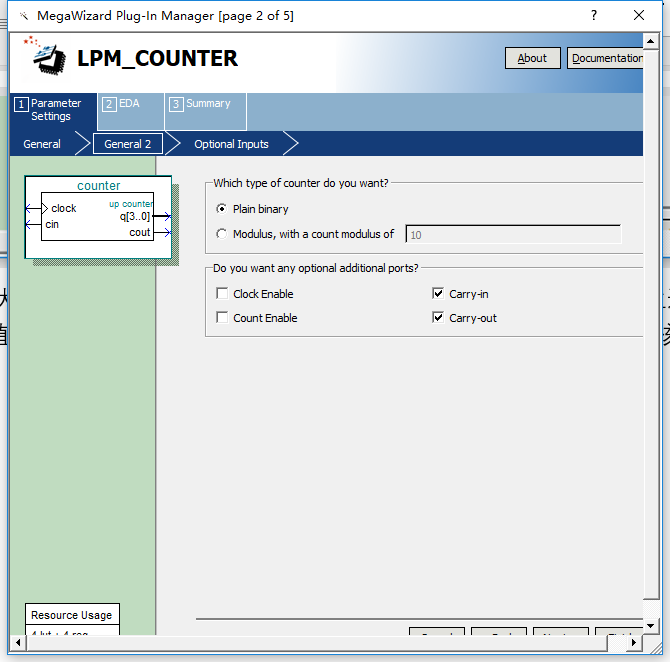

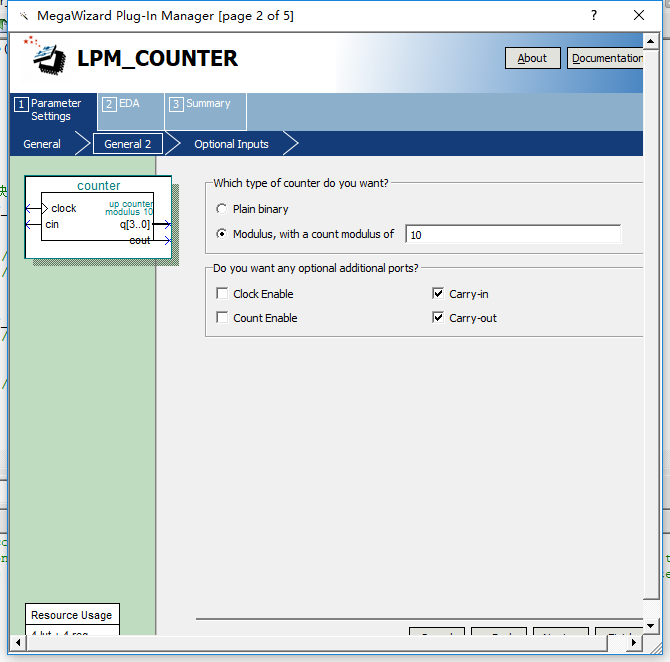

计数器IP核配置

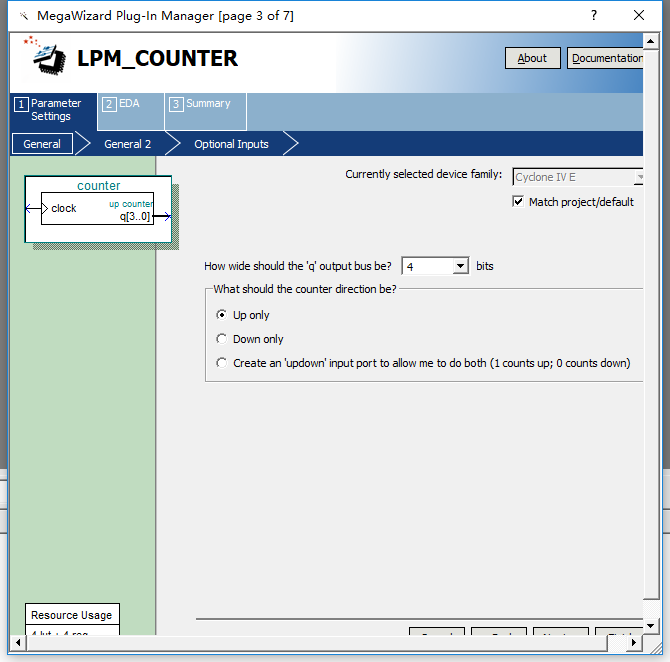

QuartusII 提供的LPM_counter IP核的使用

1、 选择输出是多少位

2、 选择计数方式为1向上计数2向下计数3创建一个端口选择是增计数或减计数

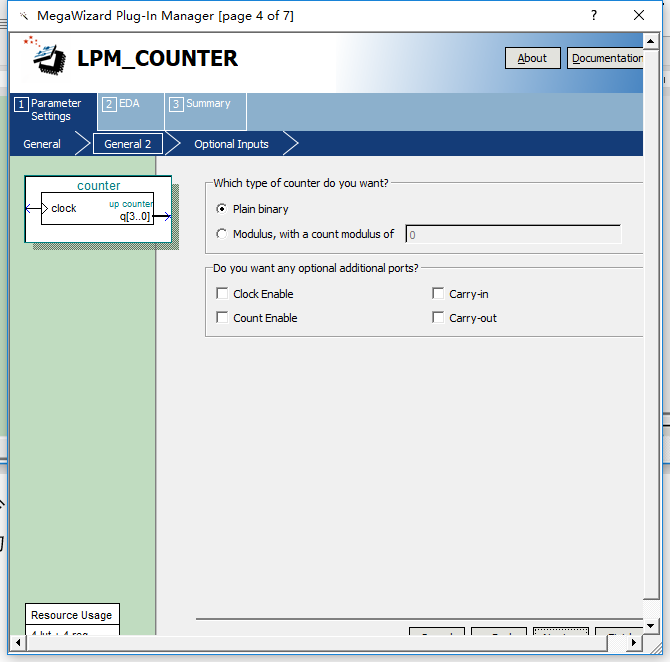

3、 选择计数器类型1直接二进制计数2模的形式,计数器计数到设置的最大值直接清零

4、 选择需要的端口1时钟使能信号2计数使能信号3进位输入:若使用这个信号,只有当进位输入有效,才会进行计数4进位输出:若使用信号,当计数结果满预设值,会输出一个进位输出。用于实现计数器级联。

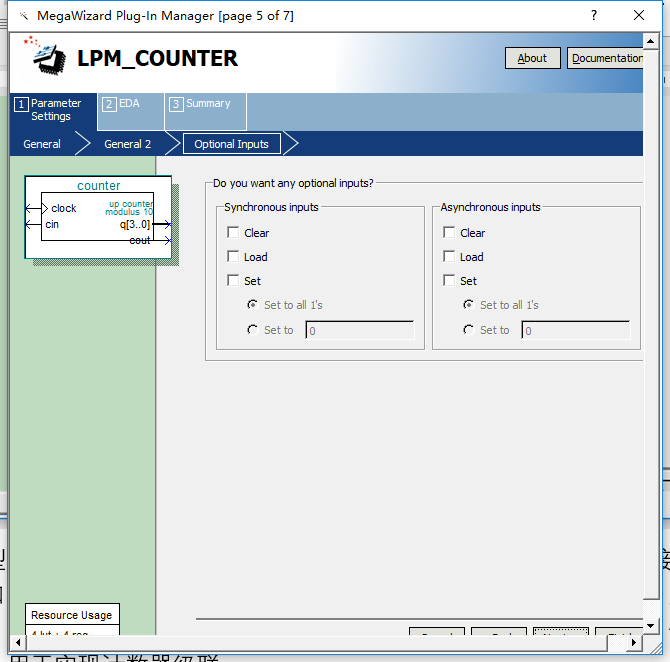

5、 清零、加载、置位选项

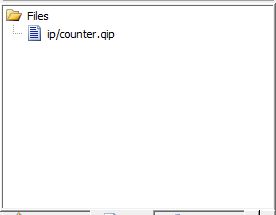

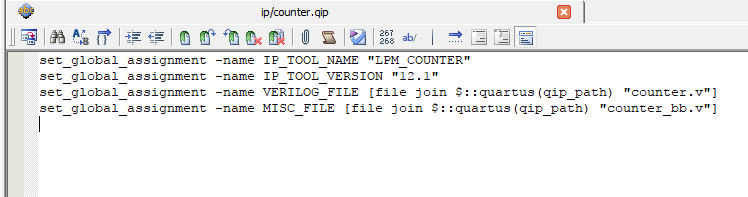

Finish后添加IP核,qip信息文件

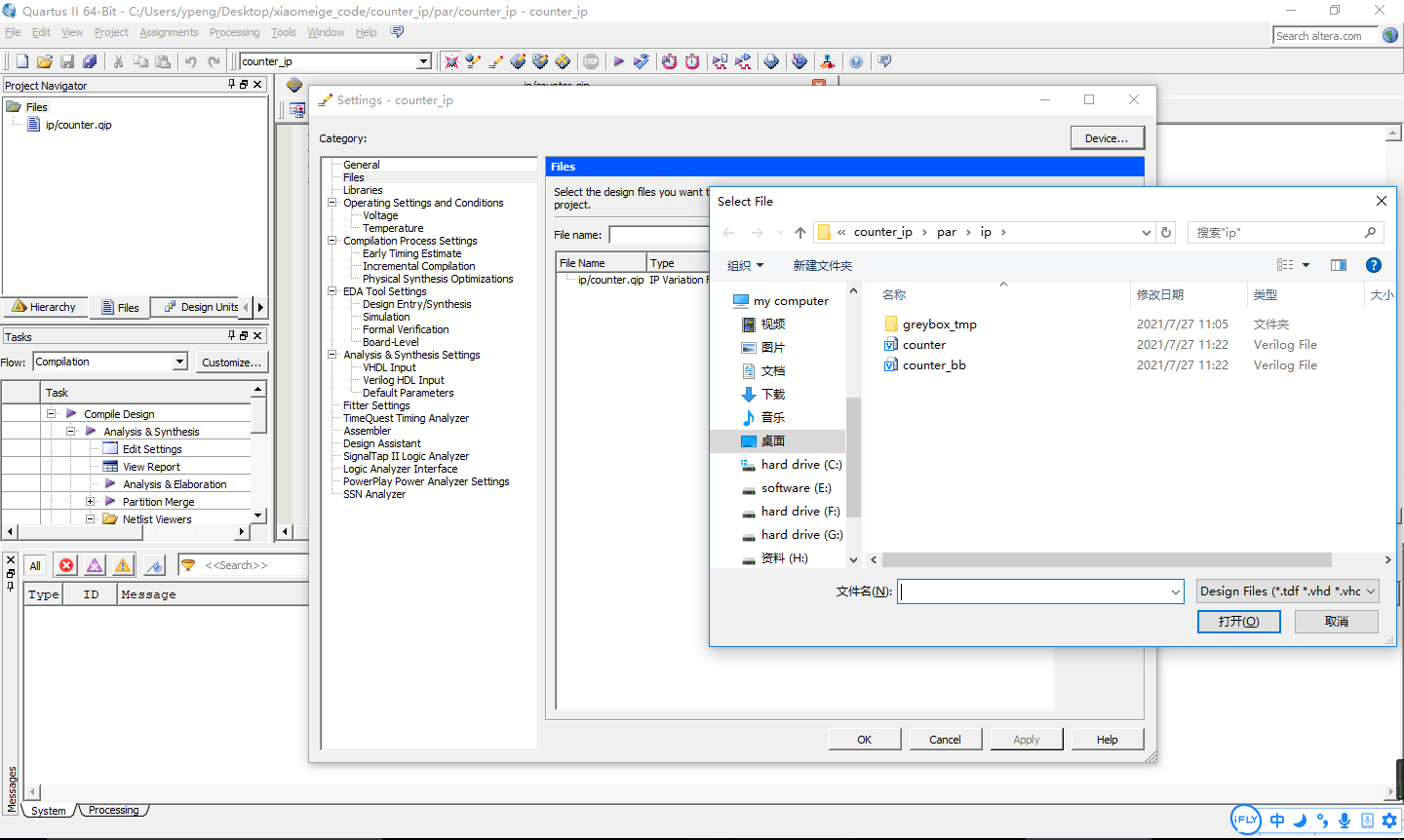

添加IP核到工程,counter.v就是需要添加等ip核文件。Counter_bb.v文件为blackbox黑盒文件,涉及到ip核具体实现有关,不需要关心。

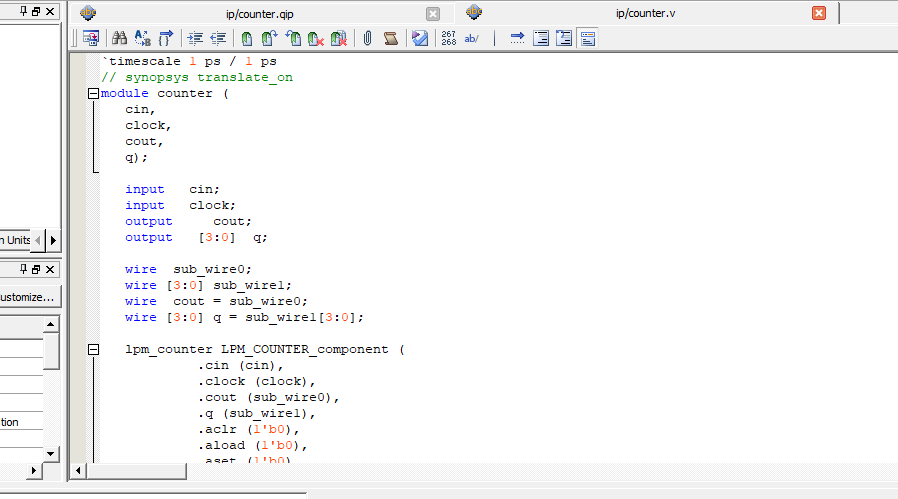

添加counter.v文件后,代码如下

对于具体内容不用关心,只需要关心端口,将端口例化到用户设计中即可。

由于counter的ip核直接就可以作为输出,可以直接将counter设置为顶层模块进行输出。

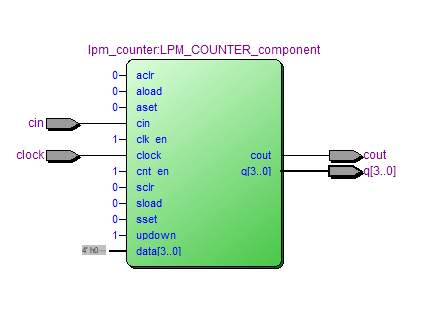

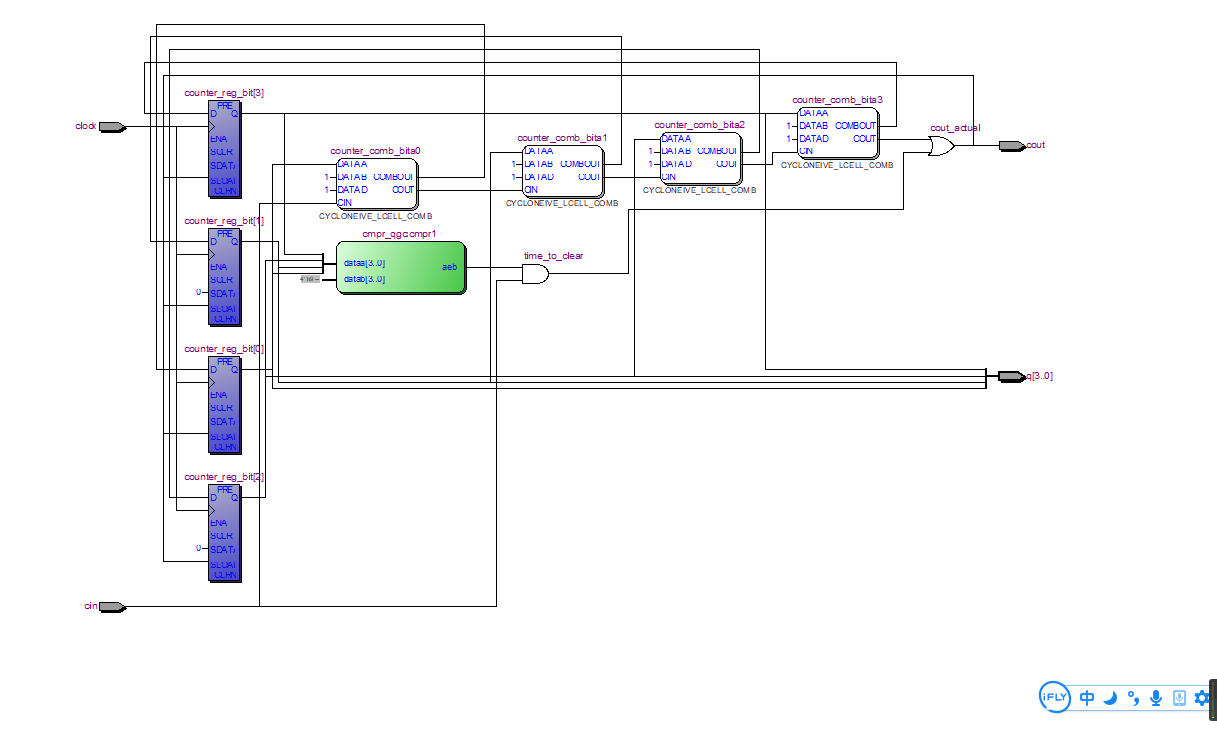

Ip核实现到硬件RTL结构

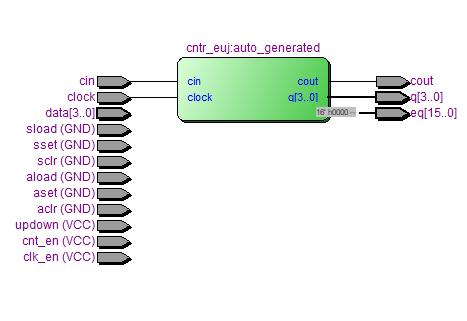

总体框图

没有使用到到引脚就会默认接地

Counter1、2、3及查找表等结构构成计数器,更加接近FPGA内部的电路结构

功能仿真

编写testbench文件

测试文件中需要给出输入计数的激励

这里每五个低电平产生一个高电平给到计数输入口,重复五次。每得到一个高电平计数器计数一次。

`timescale 1ns/1ns

`define clock_period 20//定义时钟周期,频率20ns,周期20MHz

module counter_tb;

//定位输入端口,输入端口使用reg类型

reg cin;//进位输入

reg clk;//计数基准时钟

//定位输出端口,输出端口用wire类型

wire cout;

wire [3:0] q;

counter counter_0(//模块例化,对新的测试模块命名为counter_0

.cin (cin),

.clock (clk),

.cout (cout),

.q (q)

);

//原模块名 新模块名(

//.原模块接口1 (新模块接口1),

//.原模块接口2 (新模块接口2),

//);

//初始化时钟信号

initial clk = 1 ;

always #(`clock_period/2)clk = ~clk;//每到达时钟周期到一半时,对时钟进行翻转

initial begin

repeat(20)begin//repeat重复循环5次

cin = 0 ;

#(`clock_period*5)cin = 1;//低电平保持五个时钟周期,高电平保持一个时钟周期,得到一个脉冲信号

#(`clock_period)cin = 0;

end

#(`clock_period*200);

$stop;

end

endmodule

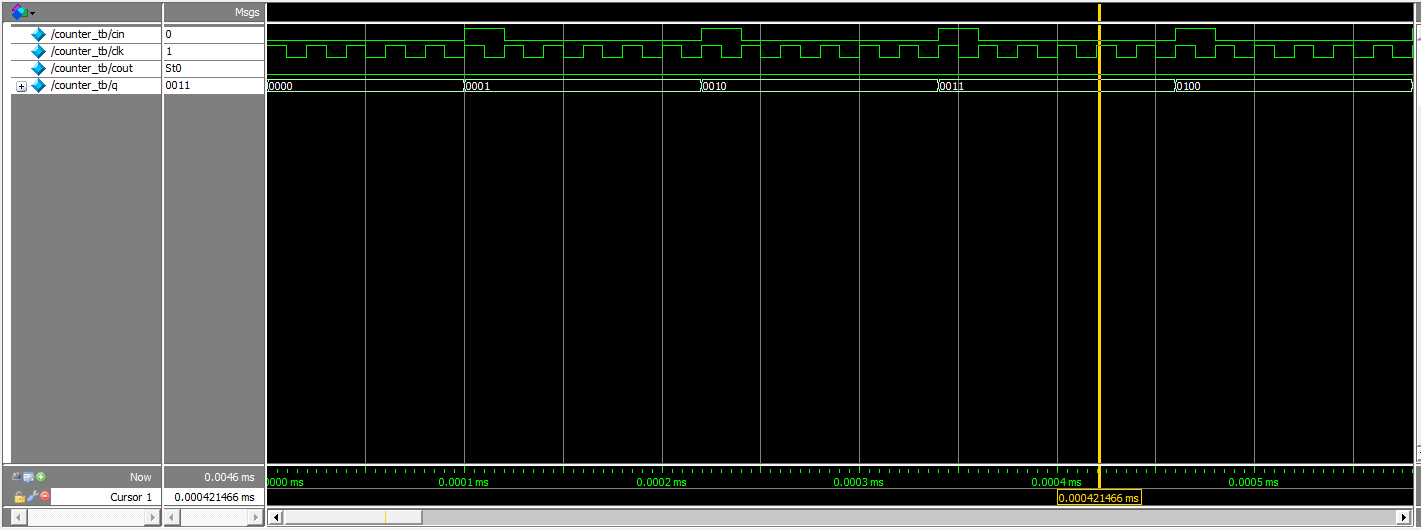

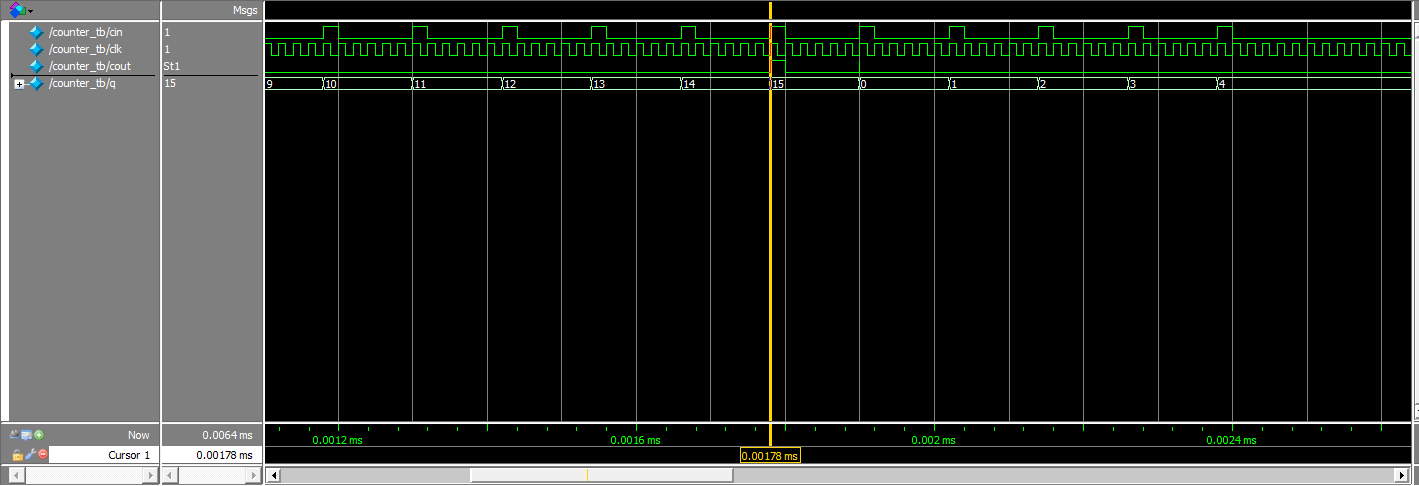

仿真结果

由于设置ip核的最大计数值为10,计数器在计数满十次,在计数到9的时候,产生进位输出,下次的计数值为0。在0的时候产生一个毛刺的情况,可能是因为计数器ip核内有布局布线产生的。

更改ip核的设置

此时的进位标志只有当计数器计满时,产生进位标志。

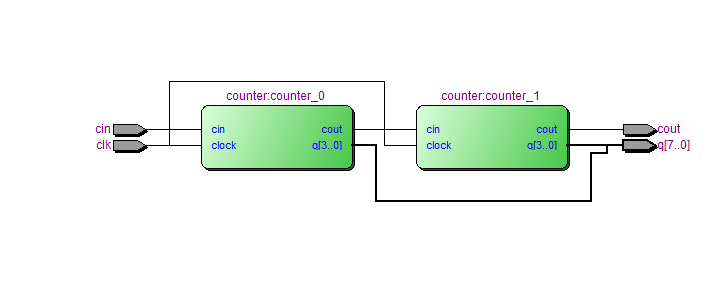

IP核调用实现计数器级联

编写顶层模块,例化两个计数器,并进行级联。

顶层模块例化代码如下

module counter_top(cin,clk,cout,q);

input cin;

input clk;

output cout;

output [7:0] q;

wire cout0;

//顶层默克进行模块例化

counter counter_0(//例化第一个模块

.cin (cin),

.clock (clk),

.cout (cout0),//低位置位信号

.q (q[3:0])//低四位输出

);

counter counter_1(//例化第二个模块

.cin (cout0),//低位置位输出连接到高位输入

.clock (clk),

.cout (cout),

.q (q[7:4])//高四位输出

);

endmodule

RTL视图如下所示。

编写顶层模块测试的testbench文件

`timescale 1ns/1ns

`define clock_period 20//定义时钟周期,频率20ns,周期20MHz

module counter_top_tb;

//定位输入端口,输入端口使用reg类型

reg cin;//进位输入

reg clk;//计数基准时钟

//定位输出端口,输出端口用wire类型

wire cout;

wire [7:0] q;

counter_top counter_0(//模块例化,对新的测试模块命名为counter_0

.cin (cin),

.clk (clk),

.cout (cout),

.q (q)

);

//原模块名 新模块名(

//.原模块接口1 (新模块接口1),

//.原模块接口2 (新模块接口2),

//);

//初始化时钟信号

initial clk = 1 ;

always #(`clock_period/2)clk = ~clk;//每到达时钟周期到一半时,对时钟进行翻转

initial begin

repeat(300)begin//repeat重复循环5次

cin = 0 ;

#(`clock_period*5)cin = 1;//低电平保持五个时钟周期,高电平保持一个时钟周期,得到一个脉冲信号

#(`clock_period)cin = 0;

end

#(`clock_period*200);

$stop;

end

endmodule

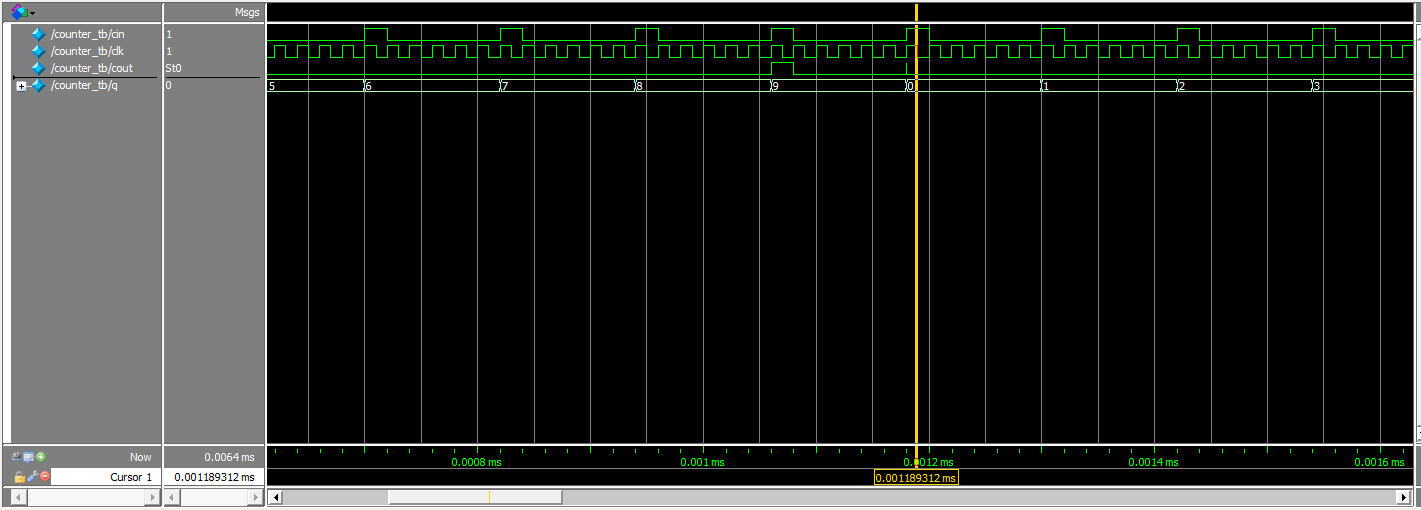

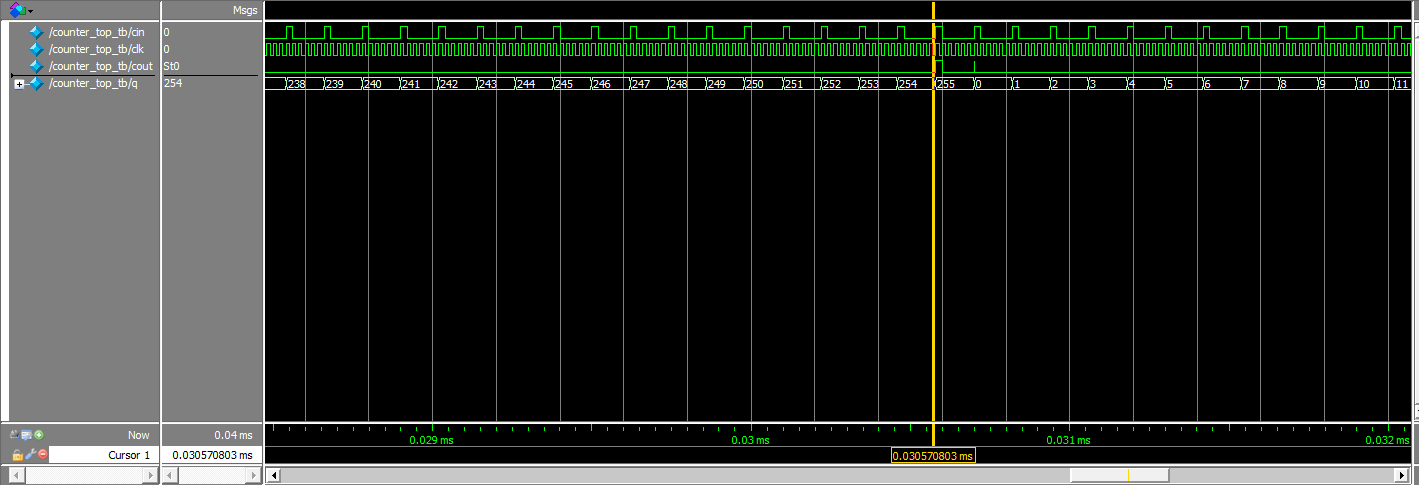

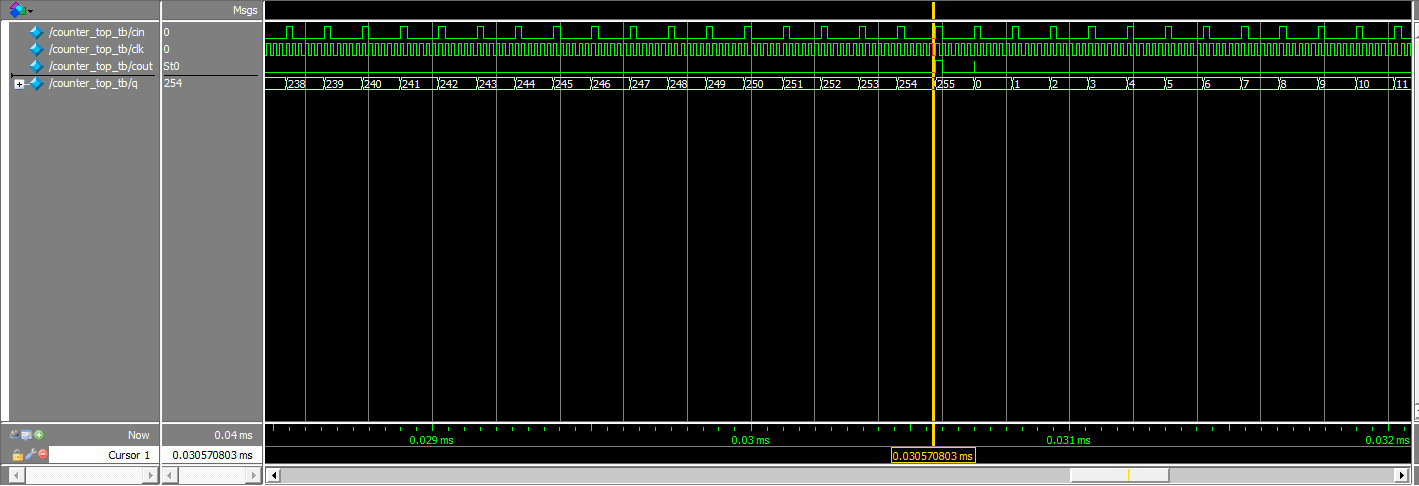

仿真结果波形

计数到255时cout输出一个脉冲信号。实现两个四位计数器级联进行计数。最高能计数到11111111(b)=255(d)

更改计数器的设置

让计数器每10产生一次输出

这样的结果是计数到153时cout输出一个脉冲,然后清零。理由:四位计数器的高四位输出为9(hex),低四位的最高输出也为9,那么输出的最大数字为99(hex)=153(d)

最后

以上就是柔弱御姐最近收集整理的关于小梅哥FPGA学习笔记——计数器IP核调用及仿真计数器IP核使用功能仿真IP核调用实现计数器级联的全部内容,更多相关小梅哥FPGA学习笔记——计数器IP核调用及仿真计数器IP核使用功能仿真IP核调用实现计数器级联内容请搜索靠谱客的其他文章。

发表评论 取消回复