本系列主要针对有限状态机进行分析和设计,其中主要包括两部分:时钟同步状态机的分析和时钟同步状态机的设计,预计会有五篇文章进行展开,其中介绍一篇,分析和设计分别有两篇,每一部分都会有相应的实例。

文章目录

- ‘SHIT’上最全有限状态机设计研究(一)-状态机介绍

- ‘SHIT’上最全有限状态机设计研究(二)-时钟同步状态机分析1

- ‘SHIT’上最全有限状态机设计研究(三)-时钟同步状态机分析2

- ‘SHIT’上最全有限状态机设计研究(四)-时钟同步状态机设计1

- ‘SHIT’上最全有限状态机设计研究(五)-时钟同步状态机设计2

- 时钟同步状态机设计

‘SHIT’上最全有限状态机设计研究(一)-状态机介绍

‘SHIT’上最全有限状态机设计研究(二)-时钟同步状态机分析1

‘SHIT’上最全有限状态机设计研究(三)-时钟同步状态机分析2

‘SHIT’上最全有限状态机设计研究(四)-时钟同步状态机设计1

‘SHIT’上最全有限状态机设计研究(五)-时钟同步状态机设计2

时钟同步状态机设计

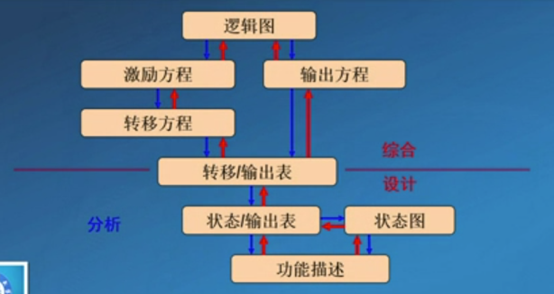

时钟同步状态机设计大致遵从如下步骤:

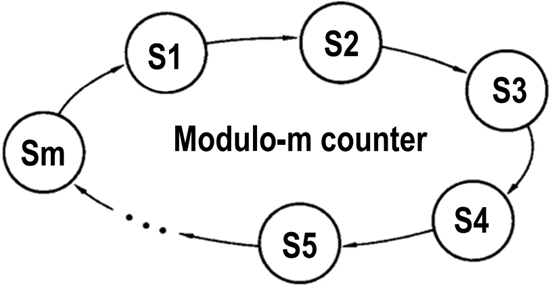

举例如下,设计一个模5的计数器。计数器的基本概念如下:

1、 没有其他输入;

2、 状态构成一个单循环;

3、 模 指循环中的状态个数。

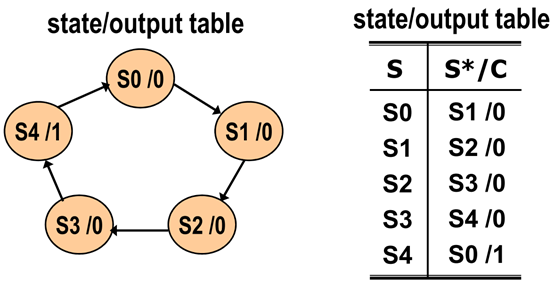

如下图所示的状态图:

按照之前图片中状态机设计的步骤开始设计。

第一步, Construct state/output diagram or state/output table(构造状态/输出图 或者 状态/输出表)

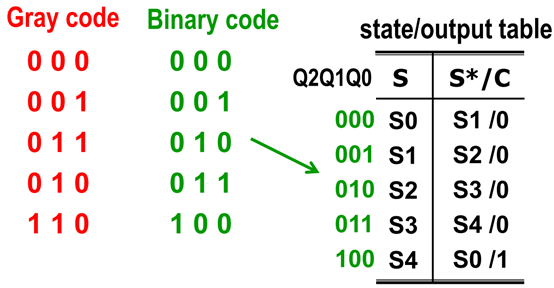

第二步,State assignment(状态分配)

本例子中状态较少,所以只选用简单的二进制编码。

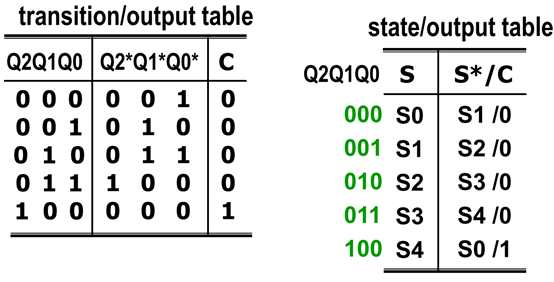

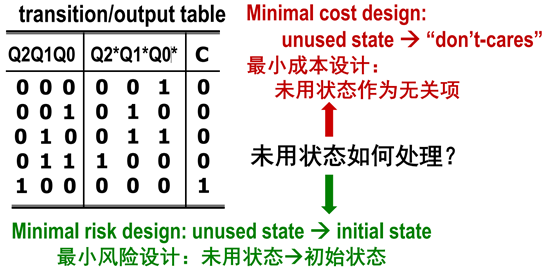

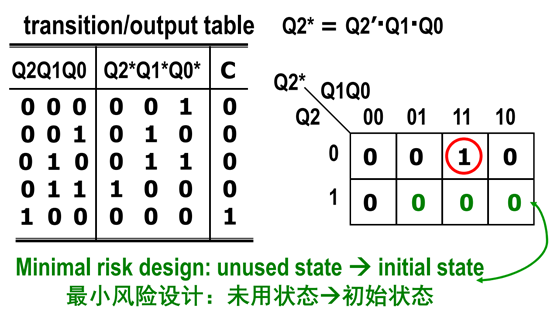

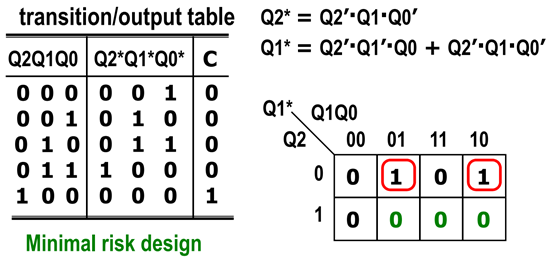

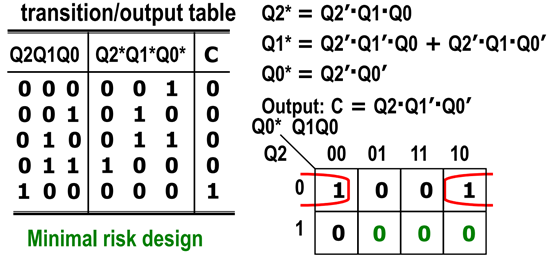

第三步,Create transition/output table(构造转移输出表),derive transition equation and output equation(导出转移方程和输出方程)

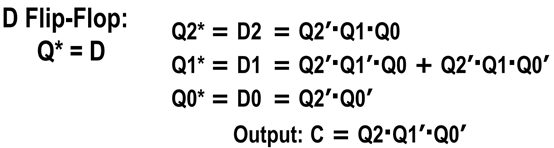

第四步,Choose flip-flop type, construct excitation equations

(选择触发器类型,构造激励方程)

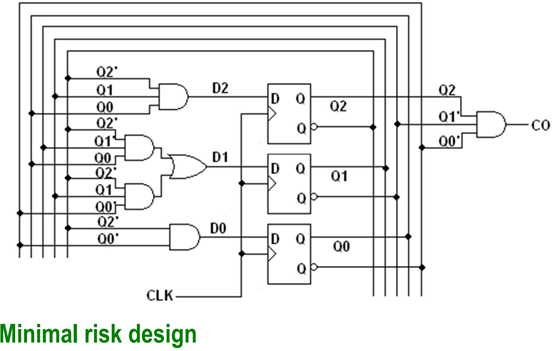

第五步,Draw a circuit diagram(绘制电路图)

过程总结

Construct state/output table(构造状态表)

State assignment(状态分配)

Create transition/output table(转移/输出表)

Derive transition equations and output equations

(导出转移方程和输出方程)

Choose flip-flop, Construct excitation equations

(选择触发器,构造激励方程)

Draw a logic circuit diagram(绘制电路图)

欢迎大家订阅我的公众号,关于FPGA相关资料和新闻我会第一时间更新到公众号中,谢谢大家!

最后

以上就是重要小虾米最近收集整理的关于‘SHIT’上最全有限状态机设计研究(四)-时钟同步状态机设计1‘SHIT’上最全有限状态机设计研究(一)-状态机介绍‘SHIT’上最全有限状态机设计研究(二)-时钟同步状态机分析1‘SHIT’上最全有限状态机设计研究(三)-时钟同步状态机分析2‘SHIT’上最全有限状态机设计研究(四)-时钟同步状态机设计1‘SHIT’上最全有限状态机设计研究(五)-时钟同步状态机设计2时钟同步状态机设计的全部内容,更多相关‘SHIT’上最全有限状态机设计研究(四)-时钟同步状态机设计1‘SHIT’上最全有限状态机设计研究(一)-状态机介绍‘SHIT’上最全有限状态机设计研究(二)-时钟同步状态机分析1‘SHIT’上最全有限状态机设计研究(三)-时钟同步状态机分析2‘SHIT’上最全有限状态机设计研究(四)-时钟同步状态机设计1‘SHIT’上最全有限状态机设计研究(五)-时钟同步状态机设计2时钟同步状态机设计内容请搜索靠谱客的其他文章。

发表评论 取消回复