本系列主要针对有限状态机进行分析和设计,其中主要包括两部分:时钟同步状态机的分析和时钟同步状态机的设计,预计会有五篇文章进行展开,其中介绍一篇,分析和设计分别有两篇,每一部分都会有相应的实例。

文章目录

- ‘SHIT’上最全有限状态机设计研究(一)-状态机介绍

- ‘SHIT’上最全有限状态机设计研究(二)-时钟同步状态机分析1

- ‘SHIT’上最全有限状态机设计研究(三)-时钟同步状态机分析2

- ‘SHIT’上最全有限状态机设计研究(四)-时钟同步状态机设计1

- ‘SHIT’上最全有限状态机设计研究(五)-时钟同步状态机设计2

- 时钟同步状态机分析Clocked Synchronous State Machine Analysis

- 2.1时钟同步状态机的描述

- 2.2时钟同步状态机的分析

‘SHIT’上最全有限状态机设计研究(一)-状态机介绍

‘SHIT’上最全有限状态机设计研究(二)-时钟同步状态机分析1

‘SHIT’上最全有限状态机设计研究(三)-时钟同步状态机分析2

‘SHIT’上最全有限状态机设计研究(四)-时钟同步状态机设计1

‘SHIT’上最全有限状态机设计研究(五)-时钟同步状态机设计2

时钟同步状态机分析Clocked Synchronous State Machine Analysis

2.1时钟同步状态机的描述

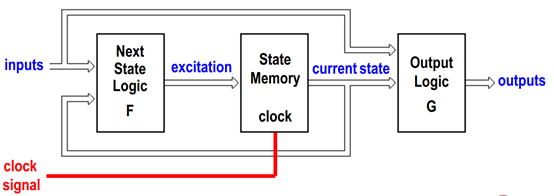

图3 时钟同步状态机的组成框图

其中,

组合逻辑电路包括:

激励=F(当前状态,输入)<–激励方程

输出=G(当前状态,输入)<–输出方程

状态转移:从Q到Q*

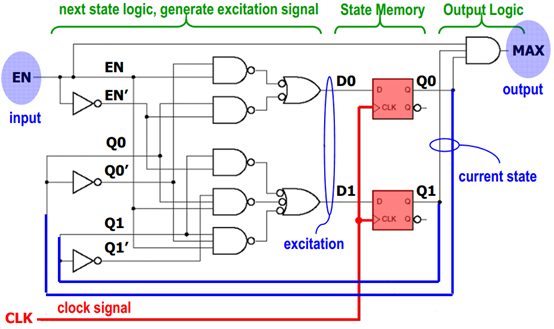

图4 状态机举例

2.2时钟同步状态机的分析

分析大致遵从如下步骤:

1)进行电路描述,得到激励方程、输出方程、转移方程;

2)构建转移/输出表(或状态转移图),描述电路功能。

如下图所示的状态图:

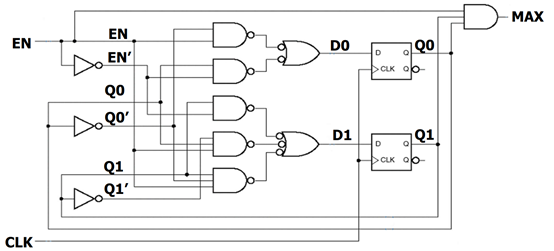

第一步,写出激励方程:

D0 = EN·Q0’ + EN’ ·Q0

D1 = EN’ ·Q1 + EN·Q1’·Q0 + EN·Q1·Q0’

第二步,写出输出方程:

MAX= EN·Q1·Q0

第三步,写出转移方程:

MAX= EN·Q1·Q0

D触发器特征方程:

Q0 = D0, Q1 = D1

将激励方程带入触发器的特征方程,得

Q0 = EN·Q0’ + EN’·Q0

Q1 = EN’·Q1 + EN·Q1’·Q0 + EN·Q1·Q0

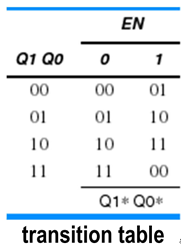

第四步,写出状态转移表:

转移表实质就是真值表,由转移表和状态表组成。

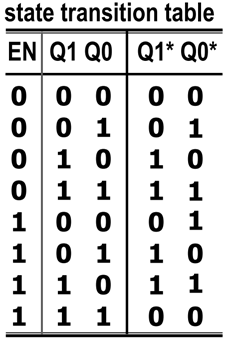

第4(1)步,转移表

由状态转移方程很好得到,从中可以看出:当EN=0保持原状态,当EN=1时表示当前变量+1操作,所以这是一个2 bit的加法计数器:

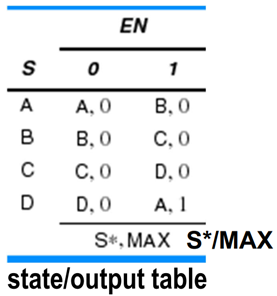

第4(2)步,状态表:

状态表和转移表的区别就是,转移表是利用状态变量的取值进行表示,状态表利用状态的变量名进行表示:

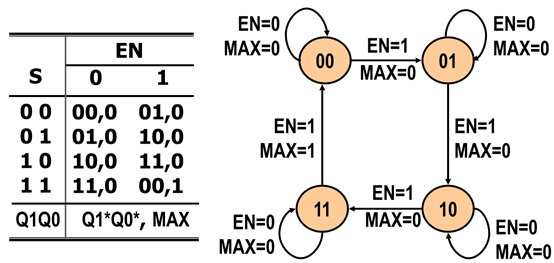

第4(3)步,状态转移表:

状态表和转移表合成就是状态转移表。

带使能端的2-bit二进制计数器 ( mealy machine )

第五步,构建状态转移图:

状态转移图,圈圈表示状态,箭头表示状态转移,箭头上标注转移和输出信息。

MAX= EN·Q1·Q0

D触发器特征方程: Q0* = D0, Q1* = D1

将激励方程带入触发器的特征方程,得

Q0* = EN·Q0’ + EN’·Q0

Q1* = EN’·Q1 + EN·Q1’·Q0 + EN·Q1·Q

欢迎大家订阅我的公众号,关于FPGA相关资料和新闻我会第一时间更新到公众号中,谢谢大家!

最后

以上就是复杂外套最近收集整理的关于‘SHIT’上最全有限状态机设计研究(二)-时钟同步状态机分析1‘SHIT’上最全有限状态机设计研究(一)-状态机介绍‘SHIT’上最全有限状态机设计研究(二)-时钟同步状态机分析1‘SHIT’上最全有限状态机设计研究(三)-时钟同步状态机分析2‘SHIT’上最全有限状态机设计研究(四)-时钟同步状态机设计1‘SHIT’上最全有限状态机设计研究(五)-时钟同步状态机设计2时钟同步状态机分析Clocked Synchronous State Machine Analysis的全部内容,更多相关‘SHIT’上最全有限状态机设计研究(二)-时钟同步状态机分析1‘SHIT’上最全有限状态机设计研究(一)-状态机介绍‘SHIT’上最全有限状态机设计研究(二)-时钟同步状态机分析1‘SHIT’上最全有限状态机设计研究(三)-时钟同步状态机分析2‘SHIT’上最全有限状态机设计研究(四)-时钟同步状态机设计1‘SHIT’上最全有限状态机设计研究(五)-时钟同步状态机设计2时钟同步状态机分析Clocked内容请搜索靠谱客的其他文章。

发表评论 取消回复