本系列主要针对有限状态机进行分析和设计,其中主要包括两部分:时钟同步状态机的分析和时钟同步状态机的设计,预计会有五篇文章进行展开,其中介绍一篇,分析和设计分别有两篇,每一部分都会有相应的实例。

文章目录

- ‘SHIT’上最全有限状态机设计研究(一)-状态机介绍

- ‘SHIT’上最全有限状态机设计研究(二)-时钟同步状态机分析1

- ‘SHIT’上最全有限状态机设计研究(三)-时钟同步状态机分析2

- ‘SHIT’上最全有限状态机设计研究(四)-时钟同步状态机设计1

- ‘SHIT’上最全有限状态机设计研究(五)-时钟同步状态机设计2

- 时钟同步状态机设计(二)序列检测器

‘SHIT’上最全有限状态机设计研究(一)-状态机介绍

‘SHIT’上最全有限状态机设计研究(二)-时钟同步状态机分析1

‘SHIT’上最全有限状态机设计研究(三)-时钟同步状态机分析2

‘SHIT’上最全有限状态机设计研究(四)-时钟同步状态机设计1

‘SHIT’上最全有限状态机设计研究(五)-时钟同步状态机设计2

时钟同步状态机设计(二)序列检测器

电路规则如下:

-

电路检测到输入端连续出现1101序列,输出为1。

-

输入:A 0011010111101101001…

-

输出:Z 0000010000001001000…

注意:1101可以重复检测

—— 用Mealy机设计

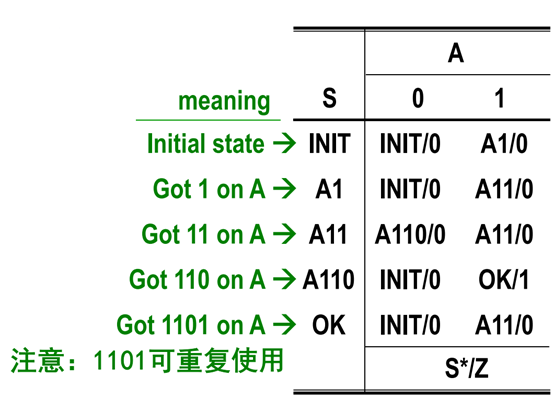

第一步,状态输出表

当前状态为S,下一状态为S*,输出为Z

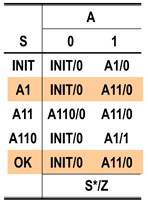

第二步,State minimization(状态化简)

Identify equivalent states,

(识别等价状态)

PS:等价状态–>如果两个状态:1)在所有输入组合下,都产生相同的输出;2)对每一个输入,都具有相同或者等效的下一个状态。

上图中两处标亮的地方具有等价状态,可以进行化简,化简后如下图所示。

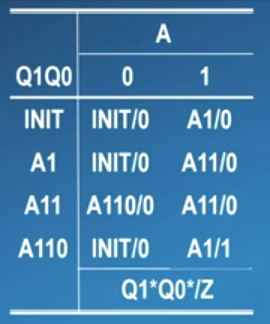

第三步,状态分配

编码采用格雷码形式,其中初始状态使用更容易进入复位状态的00表示,A1状态用01表示,A11用11表示。。。结果如下表所示:

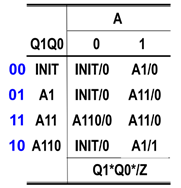

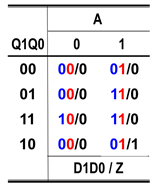

第四步,构造转移输出表:

利用复位状态的00表示,A1状态用01表示,A11用11表示。。。填入状态分配表中,就可以得到转移输出表

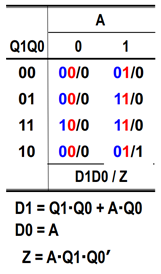

第五步,选择D触发器 导出激励方程和输出方程

由于D触发器输出输入关系为,D1=Q1* D0=Q0*,所以上表可以得到激励方程(正常情况下可以利用卡若图进行化简)

第六步,绘画出电路图(本次设计略)

欢迎大家订阅我的公众号,关于FPGA相关资料和新闻我会第一时间更新到公众号中,谢谢大家!

最后

以上就是畅快芝麻最近收集整理的关于‘SHIT’上最全有限状态机设计研究(五)-时钟同步状态机设计2‘SHIT’上最全有限状态机设计研究(一)-状态机介绍‘SHIT’上最全有限状态机设计研究(二)-时钟同步状态机分析1‘SHIT’上最全有限状态机设计研究(三)-时钟同步状态机分析2‘SHIT’上最全有限状态机设计研究(四)-时钟同步状态机设计1‘SHIT’上最全有限状态机设计研究(五)-时钟同步状态机设计2时钟同步状态机设计(二)序列检测器的全部内容,更多相关‘SHIT’上最全有限状态机设计研究(五)-时钟同步状态机设计2‘SHIT’上最全有限状态机设计研究(一)-状态机介绍‘SHIT’上最全有限状态机设计研究(二)-时钟同步状态机分析1‘SHIT’上最全有限状态机设计研究(三)-时钟同步状态机分析2‘SHIT’上最全有限状态机设计研究(四)-时钟同步状态机设计1‘SHIT’上最全有限状态机设计研究(五)-时钟同步状态机设计2时钟同步状态机设计(二)序列检测器内容请搜索靠谱客的其他文章。

发表评论 取消回复