1.存储器分类

按存储器在计算机系统中的作用:高速缓冲存储器(Cache,位于主存与CPU之间);主存;辅存

按存取方式:随机存取器(RAM,Random Access Memory,用于主存与Cache),只读存储器(ROM,Read Only Memory,随机),顺序存取器(SAM,Sequential),直接存取器(DAM,当要存取所需信息时,第一步直接指向整个存储器中的某个小区域,第二步在小区域内顺序检索)。SAM与DAM统称为串行访问存储器。

按存储介质:磁芯存储器,半导体存储器(有MOS,双极型),磁表面存储器(多辅存),光存储器(辅存)

按信息的可保存性:易失性存储器(断电后存储信息消失,半导体RAM);非易失性存储器(ROM,磁芯存储器,磁表面存储器,光存储器)。破坏性读出(信息被读出时,原信息被破坏),非破坏性读出。

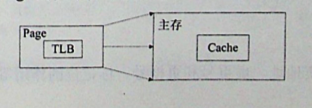

2.存储系统层次结构:Cache存储系统(Cache与主存之间,为解决主存速度不足,增加辅助硬件,对系统程序员与应用程序员都是透明的);虚拟存储系统(主存与辅存之间,为解决主存容量不足,增加软硬件,需操作系统调度,对系统程序员不透明,对应用程序员透明)

3.主存通常由存储体,地址译码驱动电路,I/O和读写电路组成

4.存储字,存储单元(存放存储字或存储字节的主存空间称为存储单元,存储单元是CPU对主存可访问操作的最小存储单位),存储体(存储单元集合)

5.大端方案,高字节在低地址,地址顺序从左到右依次变大;小端方案,高字节在高地址,地址顺序从右到左依次变大。以0x12345678为例,大端模式(0,1,2,3)->(12,34,56,78);小端模式(3,2,1,0)->(12,34,56,78)。

6.存取时间(访问时间或读写时间):启动一次存储器操作到完成该操作所经历的时间(例:读出时间是指从CPU发出有效地址和读命令开始,直到将被选单元的内容读出为止所用时间)。存取周期(读写周期,访问周期):连续2次访问存储器操作之间所用最短时间(一般情况下存取周期>存取时间,对于破坏性读出的RAM甚至存取周期=2*存取时间)。主存带宽:每秒从主存进出信息的最大数量,提高带宽措施:缩短存取周期,增加存储字长,增加存储体。

7.SRAM的存取速度快,集成度低,功耗大,用于高速缓冲存储器和小容量主存系统;DRAM存取速度慢,集成度高,功耗小,用于大容量主存系统。

8.刷新方式:集中式(刷新时间=存储矩阵行数*刷新周期,集中安排刷新时间,刷新时停止读写,这一段时间称为“死区”),分散式(存取完就刷新,增加了存取周期,刷新过于频繁,不存在死区),异步式(把刷新操作平均分配到最大刷新间隔时间内,相邻两行的刷新间隔=最大刷新间隔时间/行数)

9.刷新对CPU是透明的(由外部刷新控制电路控制或芯片内部自动);刷新通常是一行一行的,所以只需行地址,不需片选信号。

10.RAM芯片通过地址线(单向),数据线(双向)和控制线(包括读写控制线与片选线)与外部连接。DRAM采用地址复用技术,把地址分为行地址与列地址,分两次从相同引脚送入.

11.RAM地址译码方式:单译码方式,所对应存储器是字结构的,每行对应一个字,结构简单,适用于容量不大的存储器。双译码方式,K位地址线分为相等2段(X,Y),对于位结构的存储芯片4096*1,X与Y各6位,若M*b位,则把b片芯片放到Z方向,并联。

12.RAM外接引脚:地址线,数据线,片选线,读写控制线,电源线,地线。(DRAM地址线减半,但增加了行选通与列选通用以替换片选线)

13.ROM分为:MROM(掩膜式ROM,直接写入,无法更改);PROM(一次可编程ROM,用户可写入一次);EPROM(可擦除可编程ROM,用户可以多次修改,但寿命有限,写入时间比RAM长);闪速存储器(Flash Memory,不加电可保存,在线快速擦除与写)

14.ROM外接引脚:地址线,数据线,片选线,编程线,工作电源线,编程电源线,地线。

15.半导体存储器的封装:DIP存储芯片,内存条(SIMM,DIMM,RIMM),闪存(MOS管)

16.片选方法:线选法(除片内寻址外的高位地址线直接分别接至各个存储芯片;不需地址译码器,线路简单;把地址空间分成相互隔离的区域,给编程带来一定困难)。全译码法(除片内寻址外的全部高位地址线都作为地址译码器的输入,输出为片选信号;芯片的地址范围是唯一确定的,连续的;对译码电路要求较高)。部分译码(除片内寻址外的高位地址的一部分来译码产生片选信号;比全译码简单;存在地址重叠)接入各芯片地址端的是地址线的低位。

17.主存与CPU直接有三组线:地址总线(AB),数据总线(DB),控制总线(CB)。MAR可以接收来自PC的指令地址与操作数地址。MDR向主存中写入数据或读出数据的缓冲部件,MAR与MDR从功能上属于主存,但小·微型计算机常放在CPU内。

18.双通道内存技术:芯片组里制作两个内存控制器,这两个内存控制器可以是相互独立工作的,CPU可以分别寻址,读取数据,从而使内存带宽增加一倍。

19.时间局部性:如果一个存储单元被访问,可能该单元会很快被再次访问。空间局部性:如果一个存储单元被访问,该单元临近的单元很可能很快被访问。

20.Cache写操作:如果Cache命中,写直达法(数据同时写入Cache与内存;准确但会降低存取速度)与写回法(数据只写入Cache,仅当需要替换时,才把修改过的Cache块写入主存;快,但可能出错)。Cache未命中,不按写分配法(只把所要写的内容写入主存)和按写分配法(把所写内容写入主存后还把这个块从主存读入Cache中)。Cache读操作:如果Cache命中,就直接对Cache进行读操作,与主存无关;如果Cache不命中,则仍需访问主存,并把该块信息从主存调入Cache中。

21.全相联映像,让主存中任何一个块可以装入到Cache中任何位置;块冲突率最低,空间利用率最高,但慢,成本高。 直接映像:主存中每一个块只能放到Cache中唯一指定位置;块冲突率最高,空间利用率最低,但快,成本低。 组相联映像:将Cache分成大小相同的组,让主存中每一块装入对应组的任何一块位置。组间直接映像,组内全相联。

22.替换算法:随机算法,先进先出(FIFO),近期最少使用(LRU)。

23.多个Cache:增加Cache级数;将统一的Cahe变成分开的Cache(指令与数据分别存放在两个Cache中,一个叫指令Cache一个叫数据Cache)

24.虚拟存储器:程序运行时,CPU以虚地址来访问主存,由虚拟硬件找出虚地址和实地址之间的对应关系,并判断这个虚地址指示的存储单元是否已装入主存,如果已装入主存,则通过地址变换可直接访问,如果不在主存,则把包含这个字的一页或一个程序段调入主存后再由CPU实现。

25.页表,段表均存放于主存

26.段页式虚拟存储器:虚存与实存之间以页为基本传送单位,每个程序对应一个段表,每段对应一个页表。虚地址包括:段号,段内页号,页内地址。首先将段表起始地址与段号合成,得到段表地址;然后从段表中取出该段的页表起始地址,与段内页号合成,得到页表地址,最后从页表中取出实页号,与页内地址拼接形成主存实地址。

27.快表(TLB):当前最常用的页表信息存放在一个小容量的高速存储器中。快表只是慢表(存放在主存中的页表)的一个副本,且只存放了慢表中很少的一部分。

28.磁盘属于直接存储器,其速度介于随机存取存储器与顺序存取存储器之间

29.某计算机系统,其操作系统保存在硬盘上,其内存储器应采用RAM与ROM。引导程序位于ROM中,程序位于RAM。

30.直接映射的地址结构:主存字块标记,Cache字块地址,字块内地址。全相联映射:主存字块标记,字块内地址。组相联映射:主存字块标记,组地址,字块内地址

31.

32.Cache总容量包括:存储容量和标记阵列容量(有效位,标记位,一致性维护位和替换算法控制位)

最后

以上就是单身康乃馨最近收集整理的关于计算机组成原理第三章——存储系统与结构知识点摘要的全部内容,更多相关计算机组成原理第三章——存储系统与结构知识点摘要内容请搜索靠谱客的其他文章。

发表评论 取消回复