利用D触发器实现任意信号分频

我们都知道,利用D触发器可以实现分频,并且D触发器实现2的幂次方很容易,只要将它们简单的连起来就可以,那么如何利用D触发器实现任意倍数的分频呢?这里就需要对数电的知识有所了解了,这里就不阐述了,数电书翻一下就有的。

这里我举个利用D触发器实现占空比为50%的7分频,看会了这个应该可以自己实现任意的倍数分频了,好了,废话不多说,进入正题。

利用D触发器实现7分频原理

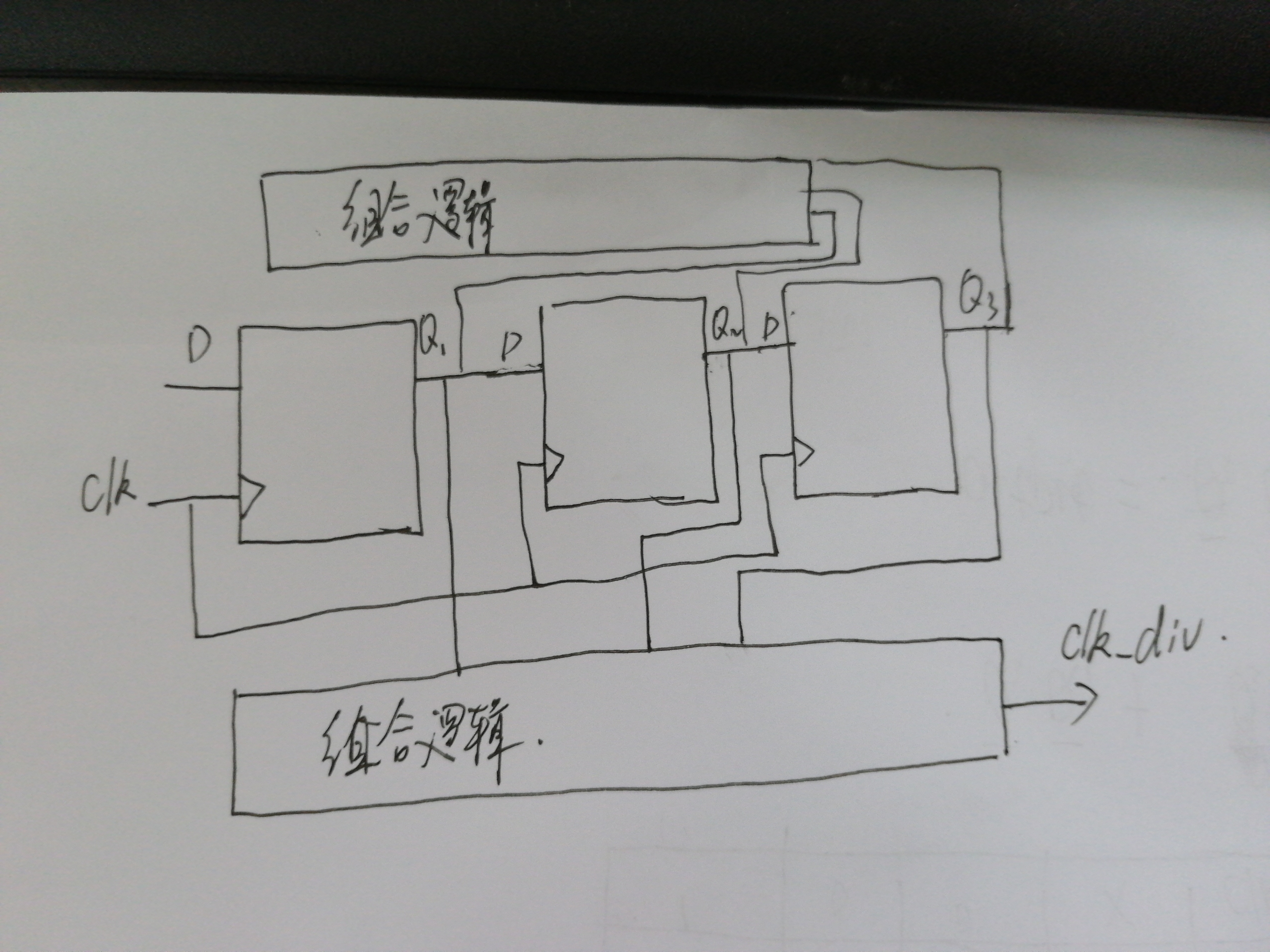

一般来说要想得到指定的分频信号,D触发器之间的连接架构是这样的,具体需要什么样的组合逻辑应该怎么得到呢,这里需要用到状态转移图。

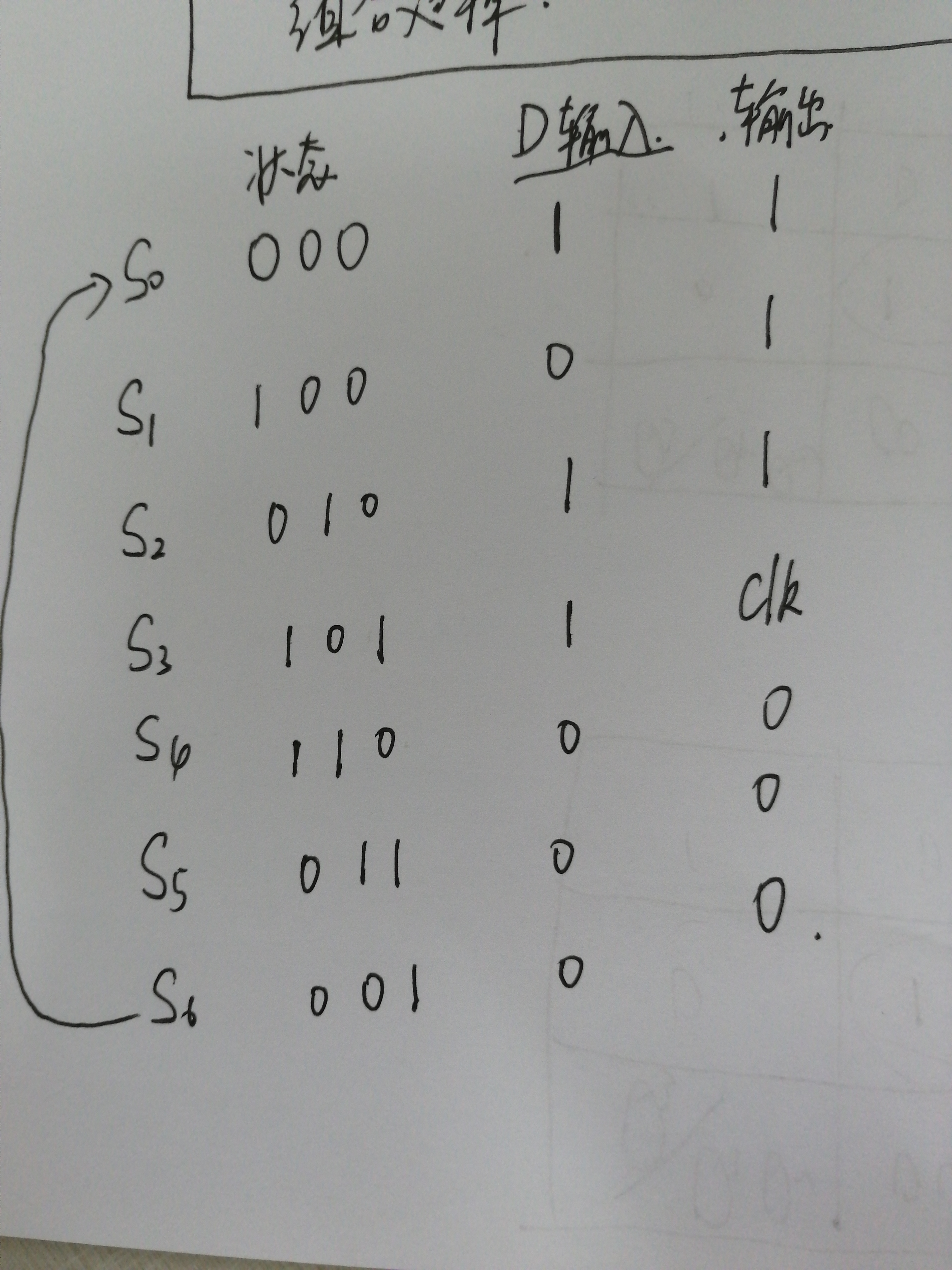

例如,我们需要得到一个七分频的信号,那我们就可以先画出状态转移图。

上述的状态转移图刚好就是个七进制的计数器,只要把输出也适当加组合逻辑变化下,就可以得到7分频的信号。

下图为上述状态转移图的卡诺图。

Verilog仿真验证

根据上述给出的输入和输出的公式,将其用Verilog来验证。以下为Verilog代码。

module D_FF(

input clk,

input rst_n,

output out

);

reg q1;

reg q2;

reg q3;

//reg D1;

//reg D2;

//reg D3;

wire in_t;

always @(posedge clk or negedge rst_n) begin

if(!rst_n) begin

q1 <= 1'b0;

end

else begin

q1 <= in_t;

end

end

always @(posedge clk or negedge rst_n) begin

if(!rst_n) begin

q2 <= 1'b0;

end

else begin

q2 <= q1;

end

end

always @(posedge clk or negedge rst_n) begin

if(!rst_n) begin

q3 <= 1'b0;

end

else begin

q3 <= q2;

end

end

assign in_t = ((~q1)&(~q3))|((q1)&(~q2)&(q3));

assign out = ((~q3)&(~q1))|((~q3)&q1&(~q2))|(q1&(~q2)&q3&clk);

endmodule

激励文件(testbench)

`timescale 1ns/1ps

module tb;

reg clk;

reg rst_n;

wire out;

D_FF D_FF_u(

.clk(clk),

.rst_n(rst_n),

.out(out)

);

initial begin

clk = 1'b0;

rst_n = 1'b1;

#100;

rst_n = 1'b0;

#100;

rst_n = 1'b1;

#10000;

$stop;

end

always #10 clk = ~clk;

endmodule

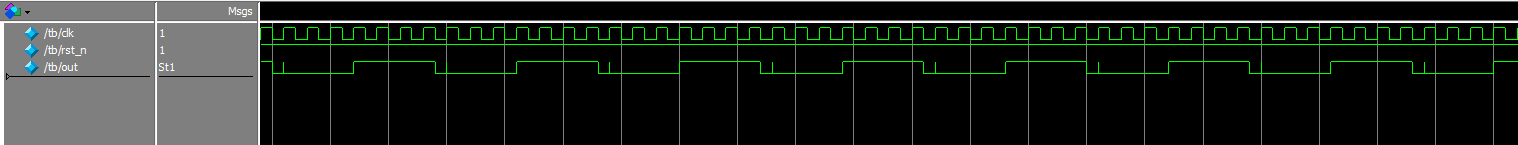

仿真结果分析

这里是行为仿真,可以看出out的高电平时间为3.5个时钟周期,低电平也是3.5个时钟周期,实现了占空比为50%的信号分配。但是我这里是行为仿真,不知道为什么会有一个毛刺,按道理说行为仿真只是验证功能的,不会出现毛刺的,如果有大神知道可以指教下。最后由于本人才疏学浅,上述内容如果有误的话,还请指正。

最后

以上就是懦弱心锁最近收集整理的关于利用D触发器实现任意倍数分频(并使用Verilog验证)的全部内容,更多相关利用D触发器实现任意倍数分频(并使用Verilog验证)内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复