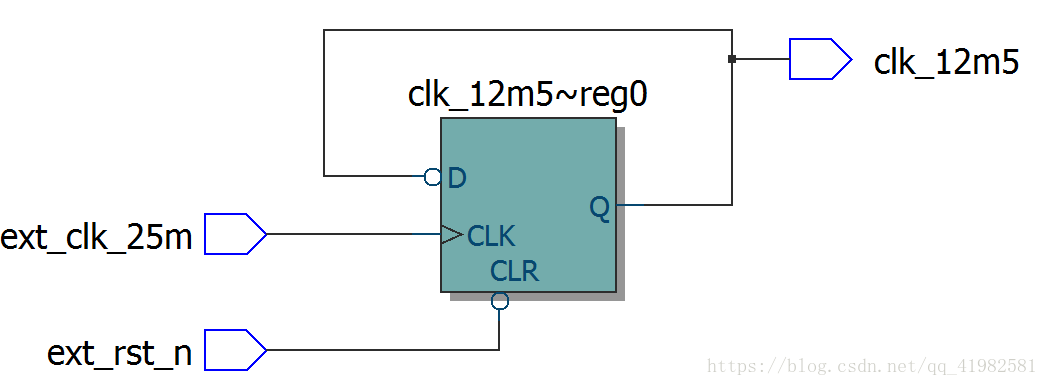

module cy4(

input ext_clk_25m, //外部输入25MHz时钟信号

input ext_rst_n, //外部输入复位信号,低电平有效

output reg clk_12m5 //二分频时钟信号

);

always @(posedge ext_clk_25m or negedge ext_rst_n)

if(!ext_rst_n) clk_12m5 <= 1'b0;

else clk_12m5 <= ~clk_12m5;

endmodule

最后

以上就是精明电源最近收集整理的关于二分频电路及代码的全部内容,更多相关二分频电路及代码内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复