本文转载自:http://www.elecfans.com/book/623/

5.4.1 D触发器电路结构与工作原理

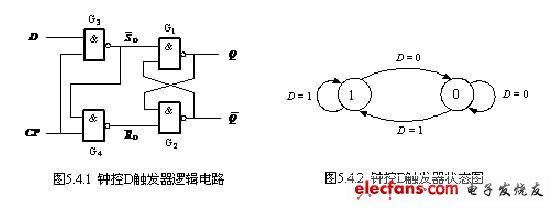

简单的钟控D触发器的逻辑电路如图5.4.1所示。它也是在基本的RS触发器的基础上发展而来的。D触发器只有一个数据端。

下面结合其电路结构分析其工作原理。

当时钟信号CP = 0时,经G3和G4与非门后,得![]() 、

、![]() ,所以D触发器得逻辑状态保持不变。

,所以D触发器得逻辑状态保持不变。

当时钟信号CP = 1时,经G3和G4与非门后,得![]() 、

、![]() ,代入基本RS触发器得特性方程可得:

,代入基本RS触发器得特性方程可得:

![]() (5.4.1)

(5.4.1)

上式即为D触发器特性方程,根据基本RS触发器约束条件:

![]()

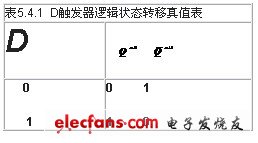

所以钟控D触发器输入端没有约束条件得限制。从式(5.4.1)的特性方程可以看出其工作得特点为:CP = 0时,触发器状态保持不变;CP = 1时,触发器的输出端接收输入端D的数据,保存在输出端。根据这一特性可以作出其状态图如图5.4.2所示,其逻辑状态转移真值表如表5.4.1所示。

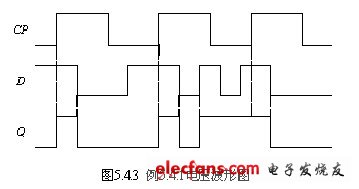

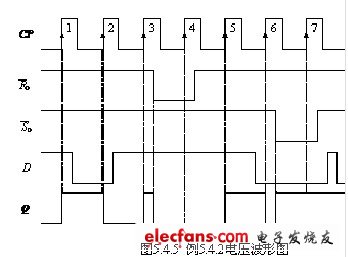

例5.4.1 在图5.4.1所示的钟控D触发器中,已知CP和D的波形如图5.4.3所示,试画出输出端![]() 的电压波形。设初始状态

的电压波形。设初始状态![]() 。

。

解:钟控D触发器的工作特点是在时钟信号为1期间,输出端根据输入端D的数据而发生变化。根据这一特点作出输出端的电压波形如图5.4.3所示。

5.4.2 边沿D触发器

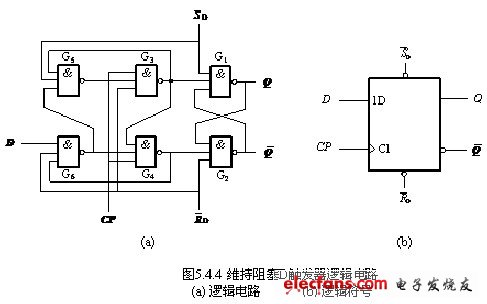

钟控D触发器同样存在CP = 1期间的多次翻转现象。只有采用边沿结构的D触发器才能解决这个问题,使输出端的值只与时钟信号边沿时刻所对应的D数据有关。图5.4.4为维持阻塞D触发器逻辑电路图和符号。

电路中![]() 、

、![]() 是异步复位、置位功能端,其作用如下:

是异步复位、置位功能端,其作用如下:

(1)当![]() 、

、![]() 时,门G2输出为1,即

时,门G2输出为1,即![]() ;同时

;同时![]() 的低电平送到了G3,则G3输出为1,G1的三个输入端都为1,G1则输出为0,即

的低电平送到了G3,则G3输出为1,G1的三个输入端都为1,G1则输出为0,即![]() ,触发器复位。

,触发器复位。

(2)当![]() 、

、![]() 时,G1输出为1,即

时,G1输出为1,即![]() ;同时

;同时![]() 的低电平送到了G5,则G5输出为1,如果CP = 1,则G3的三个输入端都为1,G3输出为0,得G4的输出为1,从而得出G2输出为0,即

的低电平送到了G5,则G5输出为1,如果CP = 1,则G3的三个输入端都为1,G3输出为0,得G4的输出为1,从而得出G2输出为0,即![]() ,如果CP = 0,G3 和G4输出都为1,得G2输出为0,即

,如果CP = 0,G3 和G4输出都为1,得G2输出为0,即![]() ,触发器置位。

,触发器置位。

从分析的结果来看,![]() 和

和![]() 的复位和置位与时钟信号CP无关,都是低电平有效。

的复位和置位与时钟信号CP无关,都是低电平有效。

![]() 、

、![]() 中没有低电平出现时,在时钟信号的边沿作用下,输出端的逻辑状态与输入端的数据D有关。其工作原理如下:

中没有低电平出现时,在时钟信号的边沿作用下,输出端的逻辑状态与输入端的数据D有关。其工作原理如下:

(1)当D= 0时

在CP= 0时,G3、G4的输出为1,G6 输出为1,G5输出为0,此低电平封锁了G3。在CP由0→1时刻,G4的输入端的时钟信号变为1,其全部的输入端都是1,所以G4输出为0,从而![]() 、

、![]() 。G4输出0送到了G6,此时即使D的数据发生变化,G6的输出也不会改变。所以将G4到G6的连线称为置0维持线。G3到G4的连线称为置0阻塞线。

。G4输出0送到了G6,此时即使D的数据发生变化,G6的输出也不会改变。所以将G4到G6的连线称为置0维持线。G3到G4的连线称为置0阻塞线。

(2) 当D= 1时

在CP= 0时,G3、G4的输出为1,G6 输出为0,此低电平封锁了G4,G5输出为1。在CP由0→1时刻,G3的输入端的时钟信号变为1,其全部的输入端都是1,所以G3输出为0,从而![]() 、

、![]() 。G3输出0送到了G5,此时即使D的数据发生变化,G5的输出也不会改变。所以将G3到G5的连线称为置1维持线。G5到G6的连线称为置1阻塞线。

。G3输出0送到了G5,此时即使D的数据发生变化,G5的输出也不会改变。所以将G3到G5的连线称为置1维持线。G5到G6的连线称为置1阻塞线。

通过上面的分析可知,由于采用了维持阻塞结构,在CP信号的上升沿到来时将D的数据送到了输出端,具有边沿触发特性,在CP信号上升沿之后,D的数据即使发生变化,也不会影响到输出端。其抗干扰能力比主从结构的触发器强。

边沿D触发器的特性方程为:

![]() 。 (5.4.2)

。 (5.4.2)

例5.4.2 在图5.4.4所示的边沿D触发器中,已知CP、D、![]() 和

和![]() 波形如图5.4.5所示,试画出输出端

波形如图5.4.5所示,试画出输出端![]() 的电压波形。设初始状态

的电压波形。设初始状态![]() 。

。

解:根据边沿D触发器的工作特点,电路中![]() 、

、![]() 是直接复位、置位功能端,与此时的CP和D信号无关,在

是直接复位、置位功能端,与此时的CP和D信号无关,在![]() 、

、![]() 同时为高电平时,时钟信号的上升沿到来时将D的数据保存到输出端。作出输出端

同时为高电平时,时钟信号的上升沿到来时将D的数据保存到输出端。作出输出端![]() 的电压波形如图5.4.5所示。

的电压波形如图5.4.5所示。

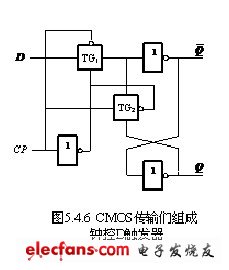

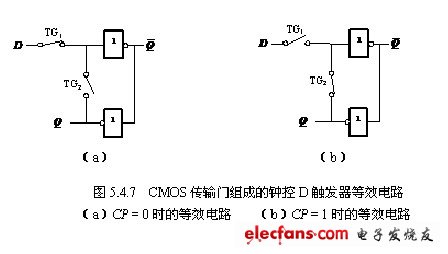

利用CMOS传输门也可以组成钟控D触发器。其电路结构如图5.4.6所示。电路由两个传输门和两个非-门组成。

当CP = 0时,TG1导通,TG2关断,此时的等效电路如图5.4.7(a)所示,触发器的输出端![]() 和

和![]() 的值与输入端D有关,即:

的值与输入端D有关,即:![]() ,

,![]() 。当CP = 0时,TG2导通,TG1关断,此时的等效电路如图5.4.7(b)所示,触发器的输出端

。当CP = 0时,TG2导通,TG1关断,此时的等效电路如图5.4.7(b)所示,触发器的输出端![]() 和

和![]() 的状态保持不变。

的状态保持不变。

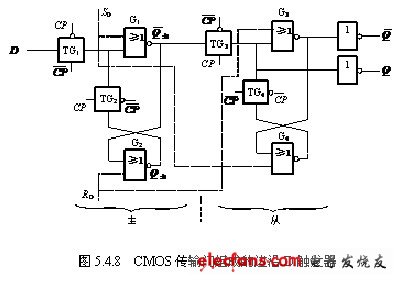

利用CMOS传输门也可以组成边沿D触发器,其电路结构如图5.4.8所示。

电路采用的是主从结构,将两个CMOS传输门组成的钟控D触发器连接而成。图中的虚线表明的是D触发器的异步复位、置位功能端RD、SD,是高电平有效复位和置位。

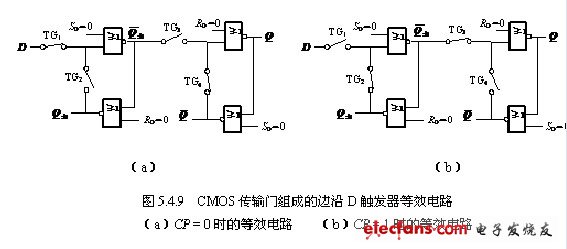

当CP = 0时,TG1导通,TG2关断,TG3关断,TG4导通,此时的等效电路如图5.4.9(a)所示,触发器的输出端![]() 跟随输入端D的数据变化而变化,而输出端

跟随输入端D的数据变化而变化,而输出端![]() 和

和![]() 的值保持不变。

的值保持不变。

当CP = 1时,TG2导通,TG1关断,TG4关断,TG3导通,此时的等效电路如图5.4.9(b)所示,触发器的输出端![]() 和

和![]() 的值取决与

的值取决与![]() 的值,也就是说在时钟信号的上升沿到来时,将主触发器的数据送到输出端保存下来,而在时钟信号下降沿前夕,

的值,也就是说在时钟信号的上升沿到来时,将主触发器的数据送到输出端保存下来,而在时钟信号下降沿前夕,![]() 的值是等于此时的输入端D的值,所以在CP由0→1时,输出端接收D的数据,也就是边沿触发器的特点。其逻辑符号如图5.4.4(b)所示。

的值是等于此时的输入端D的值,所以在CP由0→1时,输出端接收D的数据,也就是边沿触发器的特点。其逻辑符号如图5.4.4(b)所示。

最后

以上就是大力西装最近收集整理的关于【转载】门电路组成D触发器本文转载自:http://www.elecfans.com/book/623/的全部内容,更多相关【转载】门电路组成D触发器本文转载自:http://www内容请搜索靠谱客的其他文章。

发表评论 取消回复