同步时序设计原则

同步设计是 PLD ASIC 设计的最重要原则。首先阐释为什么在 PLD 设计中要采用同步时序设计,然后重点论述同步时序设计的要点。

本文内容为阅读一些书籍的摘录内容,仅供参考。

一、异步时序设计与同步时序设计

简单比较 异步电路和同步电路的异同。

1.异步电路

(1)电路的核心逻辑用组合电路实现,比如异步的FIFO/RAM读写信号、地址译码等电路.

(2)电路的主要信号、输出信号等并不依赖于任何一个时钟性信号,不是由时钟信号驱动触发器(FF)产生的.

(3)异步时序电路的最大缺点是容易产生毛刺。在布局布线后仿真和用高分辨率逻辑分析仪观测实际信号时,这种毛刺尤其明显.

(4)不利于器件移植,包括FPGA 器件族之间的移植和从FPGA向结构化ASIC的移植。

(5)不利于静态时序分析(STA)和验证设计时序的性能。

2.同步时序电路

(1)电路的核心逻辑用各种各样的触发器实现。

(2)电路的主要信号、输出信号等都是由某个时钟沿驱动触发器产生的

(3)同步时序电路可以很好地避免毛剌。布局布线后仿真和用高速逻辑分析仪采样实际工作信号时皆无毛刺。

(4)有利于器件移植,包括FPGA 器件族之间的移植和从FPGA向结构化ASIC的移植.

(5)有利于静态时序分析(STA)和验证设计时序的性能。

早期 PLD 设计经常使用行波计数器(Ripple Counters) 或者异步脉冲生成器等典型的异步逻辑设计方式,以节约设计所消耗的面积资源。但是异步逻辑设计的时序正确与否完全依赖于每个逻辑元件和布线的延时,所以其时序约束相对繁杂而困难,并且极易产生亚稳态、毛刺、造成设计稳定性下降和设计频率不高等问题。随着数字逻辑的不断经济化,器件资源已经不再成为设计的主要矛盾,而同步时序电路对全面提高设计的频率和稳定性至关重要,从这个层面上讲,同步时序电路更为重要。

另一方面,随着 PLD ASIC 逻辑规模的不断扩大,在芯片中完成复杂且质量优良的异步时序设计过于费时费力,其所需调整的时序路径和需要附加的相关约束相当繁琐,异步时序方法是与可编程设计理念背道而驰的。随着 EDA 工具的发展,大规模设计综合、实现工具的优化效果越来越强。但是目前大多数综合、实现等 EDA 工具都是基于时序驱动 CTiming Dri ven) 优化策略的。异步时序电路增加了时序分析的难度,确定最佳时序路径所需的计算量难以想象,所需的时序约束相当繁琐,而且很多综合、实现工具的编译会带来歧义。而同步时序设计则恰恰相反,其时序路径清晰,相关时序约束简单明了,综合、实现工具优化容易,布局布线计算量小。所以推荐使用同步时序设计。

综上所述,现代数字芯片设计推荐采用同步时序设计方式。

二、同步时序设计

同步时序设计的基本原则是使用时钟沿触发所有的操作。如果所有奇存器的时序要求(Setup 、Hold 时间等指标)都能够满足,则同步时序设计与异步时序设计相比,在不同的PVT (工艺、电压、温度)条件下能获得更佳的系绕稳定性与可靠性。

同步设计中,稳定可靠的数据采样必须遵从以下两个基本原则:

• 在有效时钟沿到达前,数据输入至少已经稳定了采样寄存器的 Setup 时间之久,这条原则简称为满足 Setup 时间原则;

• 在有效时钟沿到达后,数据输入至少还将稳定保持采样寄存器的 Hold 时间之久,这条原则简称为满足 Hold 时间原则。

同步时序设计有以下几个注意事项。

1.异步时钟域的数据同步

异步时钟域数据同步是芯片设计中一个常见的问题,该问题既是一个重点,也是一个难点。很多设计的不稳定都源于异步时钟域数据同步的不稳定。

(1)两类异步时钟域同步的表现形式

异步时钟域数据同步也称为数据接口同步,顾名思义,是指如何在两个时钟不同步的数据域之间可靠地进行数据交换。数据时钟域不同步的情况主要有以下两种:

• 两个域的时钟频率相同,但是相位差不固定,或者相位差固定,但是不可测,简称为同频异相问题;

• 两个时钟域频率不同,简称为异频问题。

(2)两种不推荐的异步时钟域操作方法

首先讨论两种在设计中不推荐使用的异步时钟域转换方法。-一种是通过增加 Buffer或者其他门延时调整采样;另一种是盲目使用时钟正负沿调整数据来样。

通过 Buffer 等组合逻辑延时线调整采样时间。

在早期的逻辑电路图设计阶段,设计者加入 Buffer 或者非门调整数据延时,以保证本级模块的时钟对上级模块数据的建主及保持时间的要求。这些做法目前主要应用于两种场合一种是使用分立逻辑元件(如 74 系列)搭建数字逻辑电路;另一种是在 ASIC 设计领域。

使用分立逻辑元件搭建数字逻辑电路的场合一般为系统复杂度相对较低,系统灵活性要求不高的场合。使用分立逻辑元件设计数字逻辑电路时,由于可以使用的延时调整手段较少,而且一般设计频率较低,时序余量较大,因此采用插入 Buffer 、非门等单元调整延时的手段是可以接受的。

在 ASIC 设计领域中采用这种方法是以严格的仿真和约束条件作为支持的,而在大多数数字逻辑设计,特别是在 FPGA、CPLD 等可编程逻辑设计中,这种方法是应该坚决避免的,其原因在于, Buffer 和非门等单元是组合逻辑,使用组合逻辑方法产生延时,容易产生毛刺,而且这种设计方法的时序余量较差,一旦外界条件变换(环境试验,特别是高低温试验),采样时序就可能完全紊乱,造成电路瘫痪。另外芯片更新换代,或者被移植到其他器件族的芯片,就必须对采样延时重新进行调整,电路的可维护性和继承性都很差。

盲目使用时钟正负沿调整数据采样。

很多初学者习惯随意使用时钟的正负沿来调整采样,甚至还会通过产生一系列不同相位或不同占空比的时钟来使用其正负沿调整数据,这种做法是不推荐的,原因如下。

• 第一,如果在一个时钟周期内使用时钟的双沿同时进行操作,则使用该时钟的同相倍频时钟也能实现相同的功能。换句话说,一个时钟周期内,使用时钟的双沿同时操作,相当于使用了一个同相的倍频时钟。此时由于设计的时钟频率提升,所有相关的使用约束都会变得更紧,不利于可靠实现。

• 第二,芯片中的 PLL 、DLL 一般都能较好地保证某个时钟沿的 Jitter、 Skew和占空比等各种参数指标,而对于另一个时钟沿的指标控制则并不是那么严格。特别是对于综合、实现等 EDA 软件来说,如果没有明确对另外一个沿进行约束,那么这个沿的时序分析就不一定完善,其综合或实现结果就不一定能严格满足用户的时序要求(比如 Setup Hold 时间等),这样往往会产生在该沿操作不稳定的结果。

这里还要补充以下两点。

• 虽然使用了同一个时钟的两个沿,但是如果没有在同一个周期内同时使用双沿,则不会增加时钟频率。

• DDR、 QDR 本身就是利用了上下沿采样的原理。随着存储器件的高速发展,时钟速度已经成为存取器件的瓶颈,所以可用时钟上下 沿操作缓解对单沿 RAM时钟振荡器的要求,但是必须清楚,硬件的 DDR QDR 电路(包括 ASICDDR QDR FPGA 内嵌的 DDR QDR 电路)是专用的高速设计电路,对时钟正沿、负沿的 Jitter 、 Skew 和占空比等指标都有明确的要求,这一点与普通逻辑设计,特别是 FPGA 中的设计是截然不同的,希望读者加以区分。

(3)异步时钟域数据同步问题的解决方法

同频异相问题

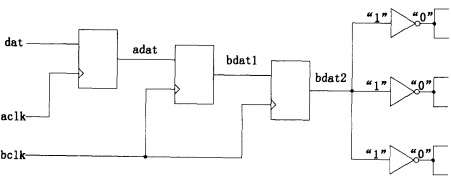

同频异相问题的简单解决方法是用后级时钟对前级数据采样两次,即通常所述的用寄存器打两次,如图所示。这种做法可以有效地减少亚稳态的传播,使后级电路数据都是有效电平值。但是这种做法并不能保证两级寄存器采样后的数据是正确的电平值,因为一旦 Setup Hold 时间不满足,采样发生亚稳态,则经决断时间后,还是可能判决到错误的电平值。所以这种方法仅仅适用于对少量错误不敏感的功能单元。

可靠的做法是用 DPRAM或 FIFO 或者一段寄存器 Buffer 完成异步时钟域的数据转换。将数据存入 DPRAM或FIFO 的方法是,将上级芯片提供的数据随路时钟作为写信号,将数据写入 DPRAM 或者 FIFO ,然后使用本级的采样时钟(一般是数据处理的主时钟)将数据读出,由于时钟频率相同, DPRAM、FIFO 两端的数据吞吐率一致,因此实现起来相对简单一些。

异频问题

解决异频问题的可靠方法就是使用 DPRAM或 FIFO 。其实现思路与前面所述一致,用上级随路时钟写入上级数据,然后用本级时钟读出数据。但是由于时钟频率不同,所以两个端口的数据吞吐率不一致,设计时一定要开好缓冲区,并通过监控( Full Half Empty 等指示)确保数据流不会溢出。

2.组合逻辑的注意事项

相对复杂一些的设计都是由两部分组成的,这两个部分分别为时序逻辑( Sequential Logic) 和组合逻辑 (Combination Logic) 。同步时序设计系统中并不是不包含组合逻辑,而是要更加合理地设计、划分组合逻辑。下面将介绍组合逻辑设计的一些问题。

(1)always 组合逻辑信号敏感表

时序逻辑的信号敏感表比较好写,只要在信号敏感表中写明时钟信号的正负触发沿即可 信号敏感表的主要问题集中在组

合逻辑信号敏感表的写法上。

• 正确的信号敏感表设计方法是将 always 模块中使用到的所有输入信号和条件判断信号都列在信号敏感表中。

• 希望通过信号敏感表的增减完成某项逻辑功能是大错特错的。

• 不完整的信号敏感表有时会造成综合前的仿真结果与综合后仿真、布局布线后仿真的结果不一致。

一般综合工具对于不完整的信号敏感表的默认做法是,将处理进程中用到的所有输入和判断条件信号都默认添加到综合结果的信号敏感表中,并发出警告(warning) 信息,提示用户该进程的信号敏感表不完整。

有些初学者发现在信号敏感表中增减一些信号,会得到不同的仿真结果,于是企图依靠修改信号敏感表来完成某些逻辑设计,这种做法是大错特错的。其实一般综合工具的默认操作都是将 always 模块中使用到的所有输入信号和条件判断信号当做触发信号,综合到信号

敏感表中。所以增减信号敏感表后得到的综合结果其实是完全一致的。之所以在增减信号敏感表后得到不同的仿真结果,是因为仿真器的工作机制所致,大多数仿真器是由数据流和时钟周期驱动的,如果信号敏感表中没有某个信号,则无法触发和该信号相关的仿真进程,从

而得到不同的仿真结果。

(2)组合逻辑反馈环路

组合逻辑反馈环路是数字同步逻辑设计的大忌,它最容易因振荡、毛刺、时序违规等问题引起整个系统的不稳定和不可靠。

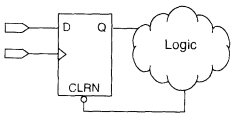

如图 所示即为一个典型的组合逻辑反馈环路,寄存器的Q 输出端直接通过组合逻辑反馈到寄存器的异步复位端,如果Q 输出为 0,经组合逻辑运算后为异步复位端有效,则电路将会进入不断清零的死循环。

组合逻辑反馈环路是一种高风险的设计方式,主要原因如

• 组合反馈环的逻辑功能完全依赖于其反馈环路上组合逻辑的门延时和布线延时等,如果这些传播延时有任何改变,则该组合反馈环单元的整体逻辑功能将彻底改变,而且改变后的逻辑功能很难确定。

• 组合反馈环的时序分析是无穷循环的时序计算,综合、实现等 EDA 工具迫不得已一般必须主动割断其时序路径,以完成相关的时序计算。而不同的 EDA工具对组合反馈环的处理方法各不相同,所以组合反馈环的最终实现结果有很多不确定因素。

同步时序系统中应该避免使用组合逻辑反馈环路,具体操作方法要有以下两种。

• 牢记任何反馈环路必须包含寄存器。

• 检查综合、实现报告的 Warning 信息,发现 Combinational Loops 后立即进行相应的修改。

3.时钟设计的注意事项

时钟是同步设计的基础,在同步设计中,所有操作都是基于时钟沿触发的,所以时钟的设计对于同步时序电路来说非常重要。在 PLD 设计中,通常推荐使用 FPGA 内嵌的 PLL、DLL 做时钟的频率与相位变化,并用全局时钟和专用时钟选择器进行时钟布线。而在ASIC设计中,常会用到各种各样的组合逻辑所产生的时钟,但是如果将这些设计直接移植到同步时序电路中,则将带来各种各样的问题。

(1)内部逻辖产生的时钟

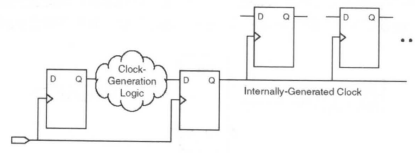

如果需要使用内部逻辑产生时钟,则必须要在组合逻辑产生的时钟后插入寄存器,如图所示。如果直接使用组合逻辑产生的信号作为时钟信号或者异步置位/复位信号,则将使设计不稳定。这是因为组合逻辑难免会产生毛刺,如果这些毛刺仅仅存在于同步时序的数据路径中,则寄存器采样会对毛刺产生过滤效应, 一般来说负面影响并不大。但是当带有毛刺的信号作为时钟信号或者异步置位/复位信号时,如果毛刺的宽度足以驱动寄存器的时钟端或者异步置位/复位端,则必将产生错误的逻辑操作,即使毛刺的宽度不足以驱动时钟端或异步置位/复位端,也会引发寄存器的不稳定,甚至激发寄存器产生亚稳态。所以对于时钟路径来说,必须插入寄存器以过滤毛刺。

另一方面,组合逻辑产生的时钟还会带来另外一个问题,组合逻辑电路的 Jitter、 Skew都比较大,如果时钟产生逻辑的延时比数据路径的延时更大,则会带来负的 Skew 。负的Skew 对于同步逻辑设计而言是灾难性的。所以使用组合逻辑来产生内部时钟仅仅适用于时钟频率较低、时钟精度要求不高的情况。另外,这类时钟应该使用快速布线资源布线,而且需要为组合逻辑电路附加一定的约束条件,以确保时钟质量。

(2)时钟选择

在通信系统中,为了适应不同的数据速率要求,经常要进行时钟切换。有时为了节约功耗,可能也会把高速时钟切换为低速时钟,或者进行时钟休眠操作。切换时钟的最佳途径是使用芯片内部专用的 Clock MUX 这些 MUX 的反应速度快,锁定时间短,切换瞬间带来的冲击和抖动小。如果所需器件没有专用的 ClockMUX ,那么在进行时钟切换时应注意以下几点。

• 时钟切换控制逻辑在配置后将不再改变。

• 切换时钟后,将所有相关电路复位,以保证所有寄存器、状态机和 RAM 等电路的状态不会锁死或进入死循环。

• 设计系统对时钟切换过程中出现的短暂错误不敏感。

(3)门控时钟

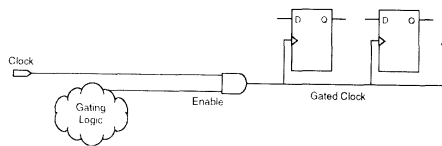

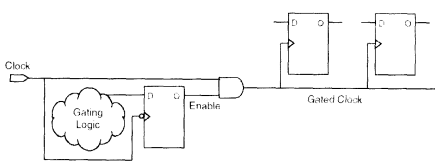

门控时钟即 Gated CIock ,如图 所示,是 IC 设计中一种常用的减少功耗的手段。设计者通过对 Gating Logic 的控制,可以控制门后端的所有寄存器不再翻转,从而有效地节约功耗。

但是 Gated Clock 不是同步时序电路,其 Gating Logic (门控逻辑)会污染 Clock 的质量,产生毛刺,并使时钟的 Skew (偏斜)、 Jitter (延时)等指标恶化。正如 "同步设计原则"所述,在同步时序电路中,应该尽量不使用 Gated Clock

虽然有时指出当功耗成为主要矛盾时,可以使用如下图所示的电路完成类似门控时钟的功能,虽然这个改进电路已经在较大程度 解决了门控电路产生毛刺的问题,但是请注意,这个电路工作的前提是时钟源 Clock 的占空比 (Duty Cycle) 是非常理想的 50% ,如果时钟的占空比不能保证为 50% ,则会产生许多有规律的毛刺信号。另外这个电路的使用还有一个前提,那就是 Clock Enable 信号的布线 Skew 为0,否则也会产生毛刺。

如果功耗真的成为 PLD 设计的首要问题,那么建议采用其他方法减少功耗,如低核电压芯片 (Core 电压为10V)、 芯片休眠功能和 ClockMUX 等。

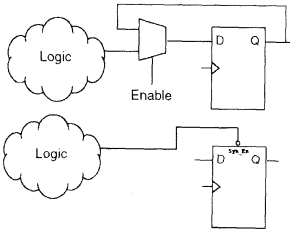

(4)时钟同步使能端

大多数像寄存器这样的同步单元都支持时钟的同步使能 (Synchronous Clock Enable)需要注意的是,虽然使能无效时这些单元无输出,但是这种方法并不能像 Gated Clock 一样减少功耗。不过 Synchronous Clock Enable 能够非常方便地完成一些逻辑功能,通过使用同步时钟使能端完成某些逻辑功能,有时可以节约芯片面积并提高设计频率。

如图上半部分所示的同步使能功能,在目前大多数的器件上可以直接将使能信号连接到芯片的同步使能端实现,如图下半部分所示。

4.同步时序电路的延时。

最常用的设计方法是用分频、倍频的时钟或者同步计数器完成所需延时。换句话说,同步时序电路的延时被当做一个电路逻辑来设计。对于比较大的和有特殊定时要求的延时来说,一般用高速时钟产生一个计数器,根据计数器的计数控制延时;对于比较小的延时,则可以用 触发器打一拍,这种做法不仅使信号延时了一个时钟周期,而且还完成了信号与时钟的初次同步,该方法通常在输入信号采样或增加时序约束余量时使用。

最后

以上就是拉长哑铃最近收集整理的关于同步时序设计原则的全部内容,更多相关同步时序设计原则内容请搜索靠谱客的其他文章。

发表评论 取消回复