四位数字电子钟设计

目录

- 四位数字电子钟设计

- 一.实验名称:四位数字电子钟设计

- 二.设计目的

- 三.设计内容

- 四.设计基本要求

- 五.器件设备

- 六.设计原理

- (1)74160引脚及其功能

- (2)74LS48引脚及其功能

- (3)74LS00引脚及其功能

- (4)数码管引脚及其功能

- (5)NE555定时器

- 七.设计过程

- 八. proteus电路图

一.实验名称:四位数字电子钟设计

二.设计目的

1.掌握数字系统设计的基本方法和流程

2.掌握计数器、译码器、数码管等常见器件的原理和使用方法

3.设计一个具有时分显示的电子钟,准确计时,设置形式显示时分,小时要求24,分钟计时要求60.

三.设计内容

本系统设计主要是有时钟译码显示数字模块,脉冲逻辑电路模块构成。计数器采用同步十进制计数器74LS160,脉冲发生器采用NE555构成。数码管译码器采用74LS48。

四.设计基本要求

本次数电课程设计的题目是“电子钟电路设计”,要求学生运用数字电路模拟电路中所学到的知识完成设计电子器件的设计

五.器件设备

74160-4片,7448-4片、NE555-1片、共阴七段数码管-4片,7400-1片、0.01uF电容-1个,68k电阻一个,10uF电容1个

六.设计原理

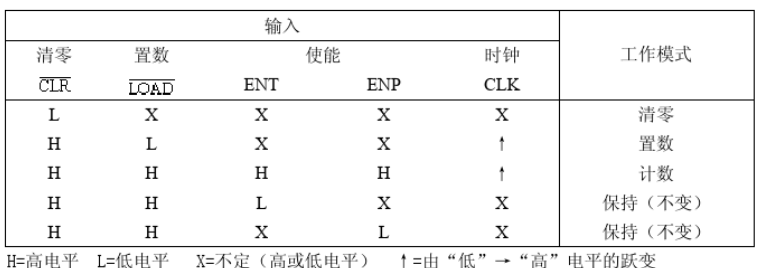

(1)74160引脚及其功能

74LS160引脚图

其引脚功能:

CLR’:清零端

CLK:时钟脉冲输入

A~D:并行输入

RCO:进位输出

QA~QD:并行输出

74LS160功能表:

这种同步可预置十进计数器是由四个D型触发器和若千个门电路构成,内部有超前进位,具有计数、置数、禁止、直接(异步)清零等功能。对所有触发器同时加上时钟,使得当计数使能输入和内部门发出指令时输出变化彼此协调一致而实现同步工作。这种工作方式消除了非同步(脉冲时钟)计数器中常有的输出计数尖峰。缓冲时钟输入将在时钟输入上升沿触发四个触发器。

这种计数器是可全编程的,即输出可预置到任何电平。当预置是同步时,在置数输入上将建立一低电平, 禁止计数,并在下一个时钟之后不管使能输入是何电平,输出都与建立数据一致。清除是异步的(直接清零),不管时钟输入、置数输入、使能输入为何电平,清除输入端的低电平把所有四个触发器的输出直接置为低电平。

超前进位电路无须另加门,即可级联出n位同步应用的计数器。它是借助于两个计数使能输入和一个动态进位输出来实现的。两个计数使能输入(ENP 和ENT)计数时必须是高电平,且输入ENT必须正反馈,以便使能动态进位输出。因而被使能的动态进位输出将产生一个高电平输出脉冲,其宽度近似等于Qa输出高电平。此高电平溢出进位脉冲可用来使能其后的各个串联级。使能ENP和ENT输入的跳变不受时钟输入的影响。

电路有全独立的时钟电路。改变工作模式的控制输入(使能ENP、ENT或清零)纵使发生变化,直到时钟发生为止,都没有什么影响。计数器的功能(不管使能、不使能、置数或计数)完全由稳态建立时间和保持时间所要求的条件来决定。

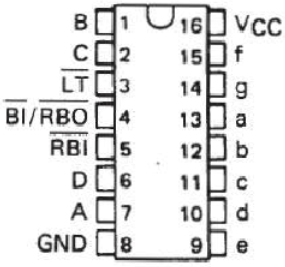

(2)74LS48引脚及其功能

74LS48引脚图:

74LS48真值表:

74LS48除了有实现7段显示译码器基本功能的输入(DCBA)和输出(Ya~Yg) 端外,7448还引入了灯测试输入端(LT)和动态灭零输入端(RBI),以及既有输入功能又有输出功能的消隐输入/动态灭零输出(BI/RBO) 端。

由7448真值表可获知7448所具有的逻辑功能:

(1) 7段译码功能(LT=1,RBI=1)

在灯测试输入端(LT)和动态灭零输入端(RBI)都接无效电平时,输入DCBA经7448译码,输出高电平有效的7段字符显示器的驱动信号,显示相应字符。除DCBA= 0000外,RBI也可以接低电平。

(2)消隐功能(BI=0)

此时BI/RBO端作为输入端,该端输入低电平信号时,无论LT和RBI输入什么电平信号,不管输入DCBA为什么状态,输出全为“0”, 7段显示器熄灭。该功能主要用于多显示器的动态显示。

(3)灯测试功能(LT = 0)

此时BI/RBO端作为输出端,端输入 低电平信号时,表1最后一行,与及DCBA输入无关,输出全为“1",显示器7个字段都点亮。该功能用于7段显示器测试,判别是否有损坏的字段。.

(4)动态灭零功能(LT=1,RBI=1)

此时BI/RBO端也作为输出端,LT端输入高电平信号,RBI端输入低电平信号,若此时.DCBA = 0000=,输出全为“0”,显示器熄灭,不显示这个零DCBA≠0,则对显示无影响。该功能主要用干名个7段显示器同时显示时熄灭高位的零。

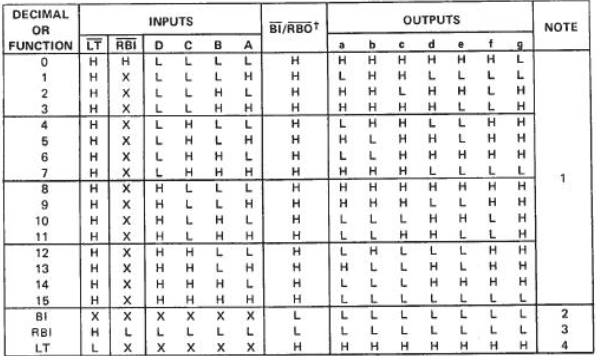

(3)74LS00引脚及其功能

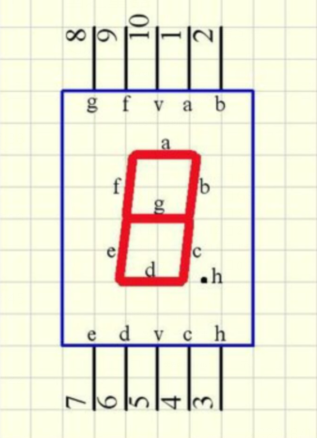

(4)数码管引脚及其功能

数码管也称LED数码管,不同行业人士对数码管的称呼不一样,其实都是同样的产品。

数码管按段数可分为七段数码管和8段数码管,八段数码管比七段数码管多一个发光二极管单元,也就是多一个小数点(DP)这个小数点可以更精确的表示数码管想要显示的内容;按能显示多少个(8)可分为1位、2位、3位、4位、5位、6位、7位等数码管。

按发光二极管单元连接方式可分为共阳极数码管和共阴极数码管。共阳数码管是指将所有发光二极管的阳极接到一起形成公共阳极(COM)的数码管,共阳数码管在应用时应将公共极COM接到+5V,当某一字段发光二极管的阴极为低电平时,相应字段就点亮,当某一字段的阴极为高电平时,相应字段就不亮。共阴数码管是指将所有发光二极管的阴极接到一起形成公共阴极(COM)的数码管,共阴数码管在应用时应将公共极COM接到地线GND上,当某一字段发光二极管的阳极为高电平时,相应字段就点亮,当某一字段的阳极为低电平时,相应字段就不亮。

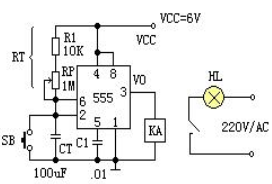

(5)NE555定时器

NE555定时器引脚功能图:

其引脚功能:

1地GND

2触发

3输出

4复位

5控制电压

6门限(阈值)

7放电

8电源电压Vcc

ne555是一种应用特别广泛作用很大的的集成电路,属于小规模集成电路,在很多电子产品中都有应用。ne555的作用是用内部的定时器来构成时基电路,给其他的电路提供时序脉冲。ne555时基电路有两种封装形式有,一是dip双列直插8脚封装,另一种是sop-8小型(smd)封装形式。其他ha17555、lm555、ca555分属不同的公司生产的产品。内部结构和工作原理都相同。

七.设计过程

数字电子钟由信号发生器、“时分”计数器、译码器以及数码管显示器电路组成,将标准脉冲信号送入“分计数器”,该计数器采用60进制计数器,每累加60分发送一个脉冲信号,该脉冲信号作为“小时计数器”的时钟脉冲。“时计数器”采用24机制金属漆,可以实现一天24h的累计。译码显示电路将十分计数器的输出状况经七段显示译码器译码,通七段数码管显示出来。

首先,画出系统ASM图

然后进行各个模块设计

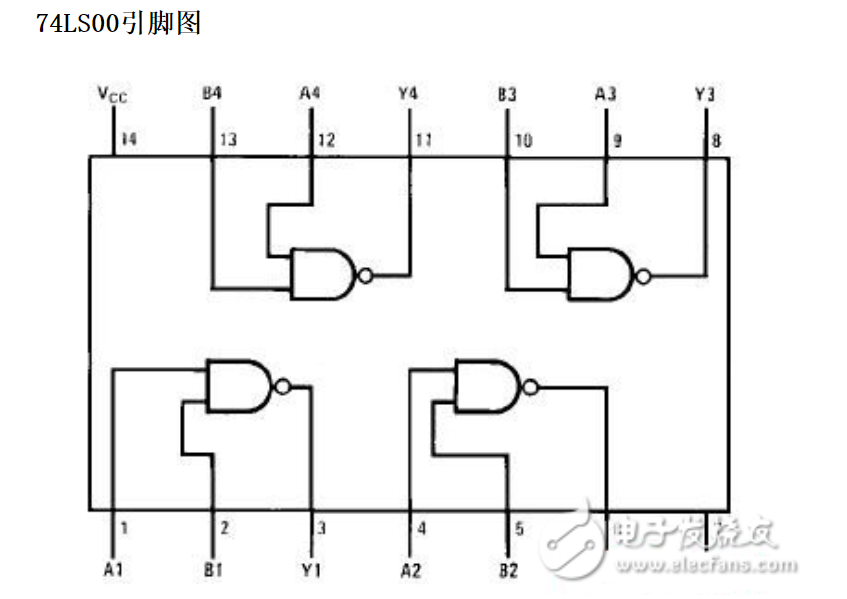

由555定时器组成一个多谐振荡器得到秒脉冲,秒脉冲输出带每个计数器始终输入端,即每个74160芯片的2引脚,再将每个74LS160芯片的四个输出端QA~QD接到74LS48的A-B四个引脚。再将74LS48的QA-QB的四个引脚输出信号接到7端数码管的信号输入引脚,从而实现4个数码管的正常计数。LS

注:将分钟个位的74LS160记为1号,将分钟十位的74LS160记为2号,将小时个位的74LS160记为3号,将小时十位的74LS160记为4号

①控制分钟的十位处的数码管进位

利用1号的进位端输出信号作为2号的ENT输入信号,2号的ENP引脚接高电平,至此完成分钟个位到十位的进位。

②控制分钟的60清零

用2号的QB,QC输出信号接入与非门,将输出信号接到2号的清零端,当十位的数跳至6时,将其清零,至此完成分钟的60进制计时。

③控制小时的个位处的数码管进位

利用1号的进位信号作为3号的ENT输入信号,2号的QA,QB信号接入与非门,再将此信号作为3号的ENT的输入信号,完成从从分钟到小时的进位计数。

④控制小时的十位处的数码管进位

利用1号的进位信号作为4号的ENT的输入信号,再将2号的QA,QC输出信号作为与非门的两个输入信号,再将此输出信号作为与非门的两个输入信号,将最后输出的信号作为4号的ENP的输入信号,完成小时的十位处的进位计数。

⑤控制小时的24清零

利用3号的QC引脚输出和4号的QB引脚输出作为与非门的两个输入信号,将此输出信号作为3号4号的清零端的输入信号,至此完成小时的24清零。

八. proteus电路图

https://download.csdn.net/download/luyaozhima/12717786

最后

以上就是彪壮曲奇最近收集整理的关于数电课设—四位数字电子钟设计四位数字电子钟设计的全部内容,更多相关数电课设—四位数字电子钟设计四位数字电子钟设计内容请搜索靠谱客的其他文章。

发表评论 取消回复