内容

实验一:7人表决器的设计

实验二:算数逻辑单元的设计

实验三:JK触发器的设计

实验四:环形计数器的设计

实验五:顺序排列的设计

实验六:二进制除法器的设计

实验七:数字显示频率计的设计

实验八:序列检测器的设计

实验九:数字秒表的设计

实验十:自助售票机的设计

实验三:JK触发器的设计

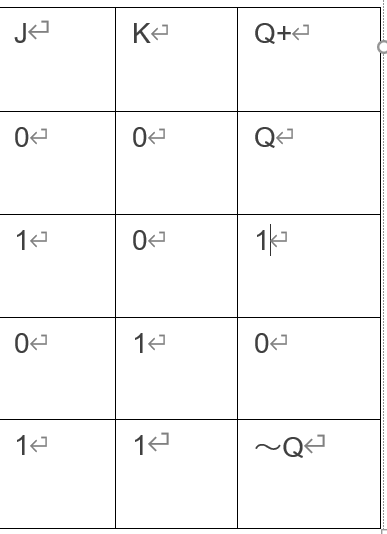

编写Verilog代码使之能正确描述下表所示的1bit JK触发器功能,其中Q+表示在时钟上升沿到来后的Q值。要求该触发器还具有异步复位的功能

//程序:

module jk_ff(q,clk,j,k,rst);

input j,k,clk;

input rst;

output reg q;

always@ (posedge clk,posedge rst)

begin

if (rst) q=0;

else

case({j,k})

2'b00 : q<= q;

2'b01 : q<= 0;

2'b10 : q<= 1'b1;

2'b11 : q<= ~q;

endcase

end

endmodule

//测试代码:

`timescale 1ns/ 1ns

module jk_tb;

reg j,k,clk,rst;

wire q;

jk_ff tb(.j(j), .k(k), .clk(clk), .q(q), .rst(rst));

always #2 clk= ~clk;

initial

begin

j= 0; k= 0;clk= 0; rst= 1'b1;

#10 rst<= 0;

#5 {j,k}<= 2'b00; #8 {j,k}<= 2'b01;

#13 {j,k}<= 2'b10; #18 {j,k}<= 2'b11;

#20 rst<= 1'b1; //测试异步复位功能

#25 {j,k}<= 2'b00; #28 {j,k}<= 2'b01;

#33 {j,k}<= 2'b10; #38 {j,k}<= 2'b11;

#40 rst<= 0;

#35 {j,k}<= 2'b00; #38 {j,k}<= 2'b01;

#43 {j,k}<= 2'b10; #48 {j,k}<= 2'b11;

#100 $stop;

end

endmodule

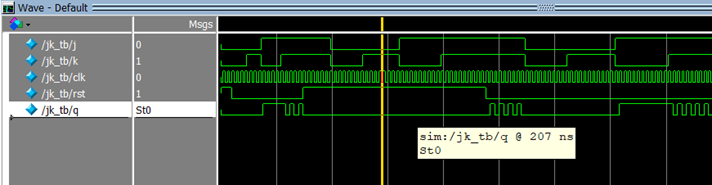

波形仿真:

结果分析:

JK触发器要实现置0、置1、保持和取反的功能,还要异步置位,设置输入变量为j, k, clk, rst, 输出为q;

在时钟上升沿JK触发器工作,将时钟上升沿写入敏感事件表,又因为需要用到异步复位功能,复位信号也要写到敏感事件表;

根据上表功能用case语句编辑函数,对应 置0、置1、保持和取反四个输出状态,将输出赋值给q。

实验四:环形计数器的设计

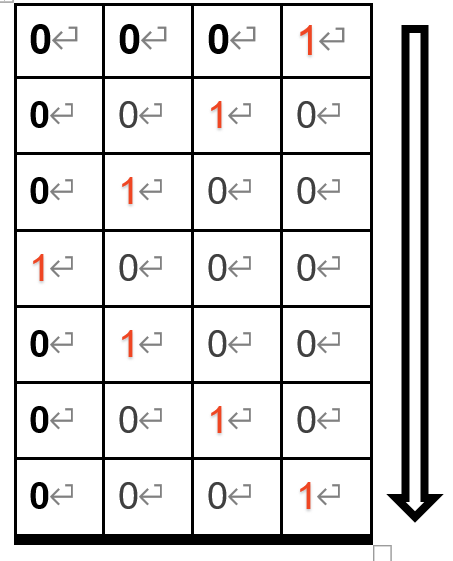

编写设计下图所示寄存顺序的环形计数器,异步复位,复位时计数器中的值为4’b0001。

要求:(1)用参数定义此计数器的位宽; (2)仿真测试对象为8bit的环形计数器

//程序:

module ring(reset,clk,count);

parameter width= 4;

input reset,clk;

output reg[width-1:0] count;

reg [3:0] i;

always@(posedge clk,negedge reset)

begin if(!reset)

begin count=4'b0001; i=0; end

else if(i<3)

begin count={count[2:0],count[width-1]}; i= i+1; end

else if(i>= 3 && i< 5)

begin count={count[0], count[width-1:1]}; i= i+1; end

else if( i>=5)

begin count = 4'b0001; i = 0;end

end

endmodule

//测试代码:

`timescale 1ns/ 1ns

module ring_tb;

reg reset,clk;

wire[3:0] count;

parameter half_clk_pried= 5;

ring u1(.reset(reset), .clk(clk), .count(count));

always #half_clk_pried clk= ~clk;

initial begin

clk = 0;

reset = 0;

#18 reset <= 1'b1;

#500 $stop;

end

endmodule

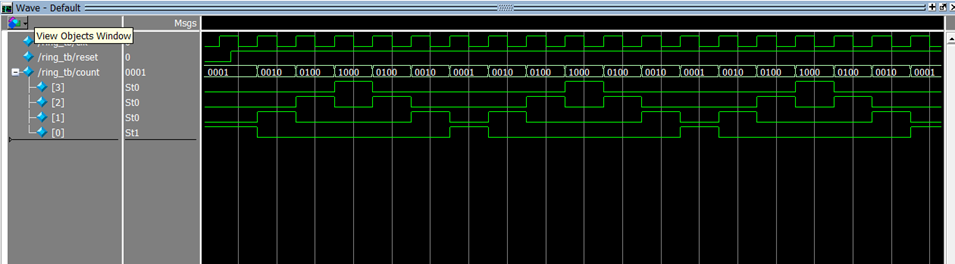

波形仿真:

结果分析:

环形计数器初始值为4’b0001,不断循环左移右移,顺序如上表所示。输入时钟信号和复位信号,输出为上表计数结果;设置一个4位用于比较的变量i,当i<3,每次左移一位,i 自加1, 当3<= i < 5, 每次右移一位, i自加1;i>= 5, 回到初始状态。在仿真过程中,在时钟上升沿信号下,实现上述计数功能。波形如下图所示。

最后

以上就是动听糖豆最近收集整理的关于基于modelsim的十个Verilog入门试验程序(2)(JK触发器+环形计数器)—程序+测试代码+波形+结果分析的全部内容,更多相关基于modelsim内容请搜索靠谱客的其他文章。

发表评论 取消回复