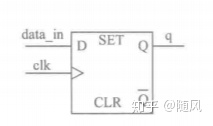

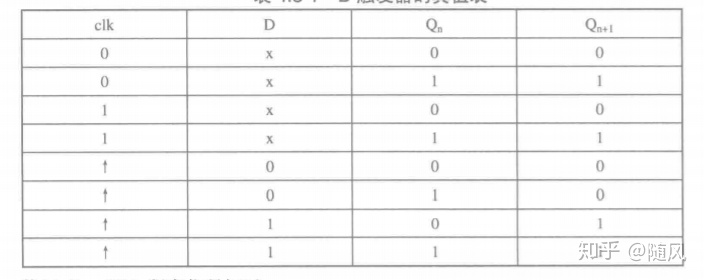

一:最简D触发器

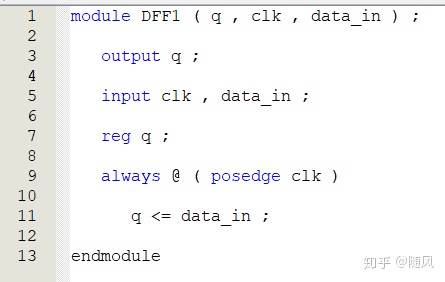

D为信号 输入端,clk为时钟控制端,Q为信号输出端。这种触发器的逻辑功能是:不论触发器原来的状态如何,输入端的数据D(无论D=0,还是D=1)都将在时钟clk的上升沿被送入触发器,使得Q=D。其特征方程可描述为Qn+1=Dn。

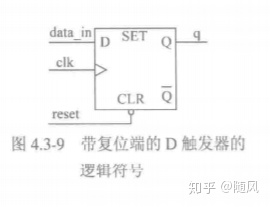

二:带复位端的D触发器

在D触发器的实际使用过程中,有时候需要一个复位端(也称清零端)

电路上电时,电路的逻辑处于不定状态,复位脉冲的到来将电路初始化为Q=0的状态。随后,在时钟的控制下输出端D的数据在每个时钟上升沿被置到输出端Q。

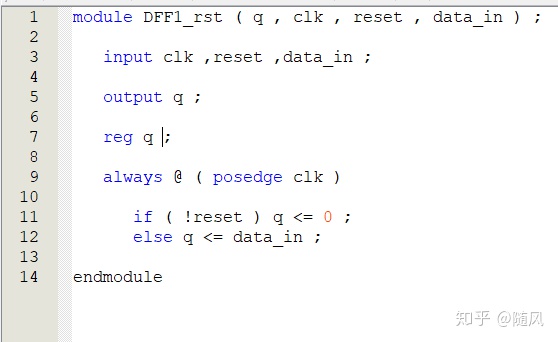

(1)同步清零代码

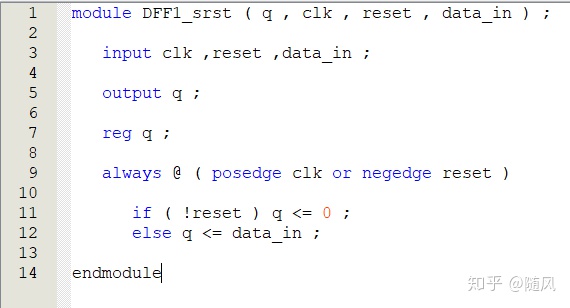

(2)异步清零代码

同步清零和异步清零触发器的电路代码只是在always后的敏感向量表上有所不同。对于同步清零,并不是清零信号一变化电路马上就会被置0,清零信号有效后需等待时钟的有效边沿到来后电路才会有动作,因此不应把清零信号写入敏感向量表中。而异步清零时,只要清零信号有效,电路就会马上更新,输出置0,因此对于异步电路,清零信号有必要写入敏感向量表中。

最后

以上就是认真冬日最近收集整理的关于双 JK 触发器 74LS112 逻辑功能。真值表_D触发器示例的全部内容,更多相关双内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复