目录

偶数分频

奇数分频

N+0.5分频

任意小数分频

偶数分频

偶数分频是最简单的,N分频需要计数到(N-1),并在(N/2 - 1)和(N - 1)处更改输出的取值即可,只需要单一时钟沿计数。下面是四分频电路的实现:

代码:

module div4(

input wire clk,

input wire rst,

output reg clk_div4

);

reg [1:0] cnt;

always @(posedge clk or posedge rst) begin

if (rst) begin

// reset

cnt <= 2'b00;

end

else if (cnt == 2'b11) begin

cnt <= 2'b00;

end

else begin

cnt <= cnt + 1'b1;

end

end

always @(posedge clk or posedge rst) begin

if (rst) begin

// reset

clk_div4 <= 1'b0;

end

else if (cnt == 2'b01) begin

clk_div4 <= 1'b1;

end

else if(cnt == 2'b11) begin

clk_div4 <= 1'b0;

end

end

endmoduletestbench:

module tb_4();

reg clk,rst;

wire clk_div4;

initial

begin

clk = 0;

rst = 1;

#5

rst = 0;

end

always #10 clk = ~clk;

div4 inst(

.clk(clk),

.rst(rst),

.clk_div4(clk_div4));

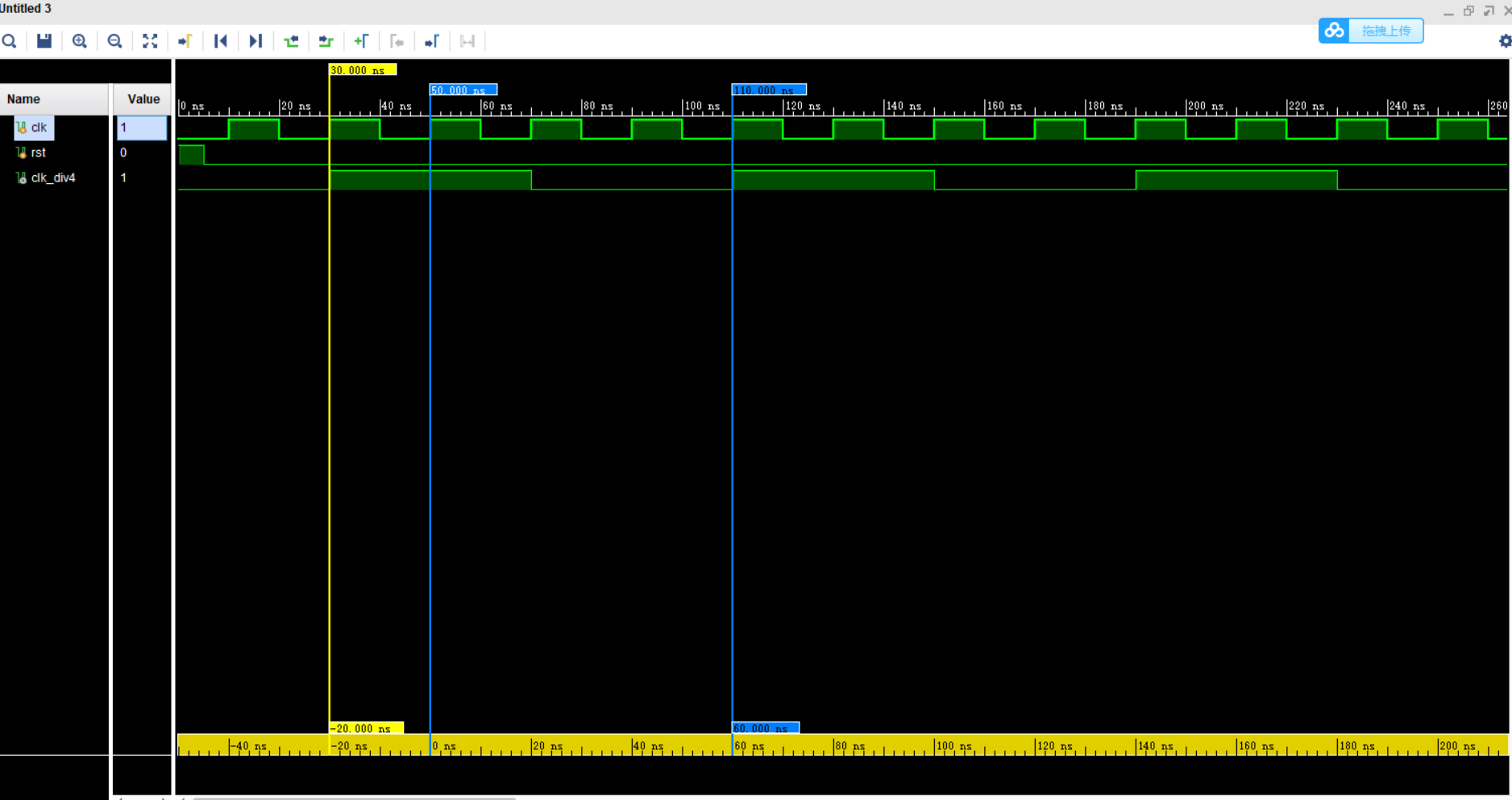

endmodule仿真波形图如下:

可以看到原来的时钟周期为20ns,4分频后周期变为了80ns。

奇数分频

奇数分频比偶数分频要复杂一些,需要在时钟的上升沿和下降沿同时计数,然后结果相或得到最终的分频输出,计数得到的上升沿触发的时钟和下降沿触发的时钟都要满足高电平比低电平少一个时钟周期,高电平保持(N-1)/2个时钟周期,低电平保持(N+1)/2个时钟周期。下面是一个7分频的实现:

module div7(

input wire clk,

input wire rst,

output wire clk_div7

);

reg clk_pos,clk_neg;

reg [2:0] cnt_pos,cnt_neg;

always @(posedge clk or posedge rst) begin

if (rst) begin

// reset

cnt_pos <= 3'b000;

end

else if (cnt_pos == 3'b110) begin

cnt_pos <= 3'b000;

end

else begin

cnt_pos <= cnt_pos + 1'b1;

end

end

always @(posedge clk or posedge rst) begin

if (rst) begin

// reset

clk_pos <= 1'b0;

end

else if (cnt_pos == 3'b011) begin

clk_pos <= 1'b1;

end

else if(cnt_pos == 3'b110) begin

clk_pos <= 1'b0;

end

end

always @(negedge clk or posedge rst) begin

if (rst) begin

// reset

cnt_neg <= 3'b000;

end

else if (cnt_neg == 3'b110) begin

cnt_neg <= 3'b000;

end

else begin

cnt_neg <= cnt_neg + 1'b1;

end

end

always @(negedge clk or posedge rst) begin

if (rst) begin

// reset

clk_neg <= 1'b0;

end

else if (cnt_neg == 3'b011) begin

clk_neg <= 1'b1;

end

else if(cnt_neg == 3'b110) begin

clk_neg <= 1'b0;

end

end

assign clk_div7 = clk_pos | clk_neg;

endmodule

testbench:

module tb_7();

reg clk,rst;

wire clk_div7;

initial

begin

clk = 0;

rst = 1;

#5

rst = 0;

end

always #10 clk = ~clk;

div7 inst(

.clk(clk),

.rst(rst),

.clk_div7(clk_div7));

endmodule

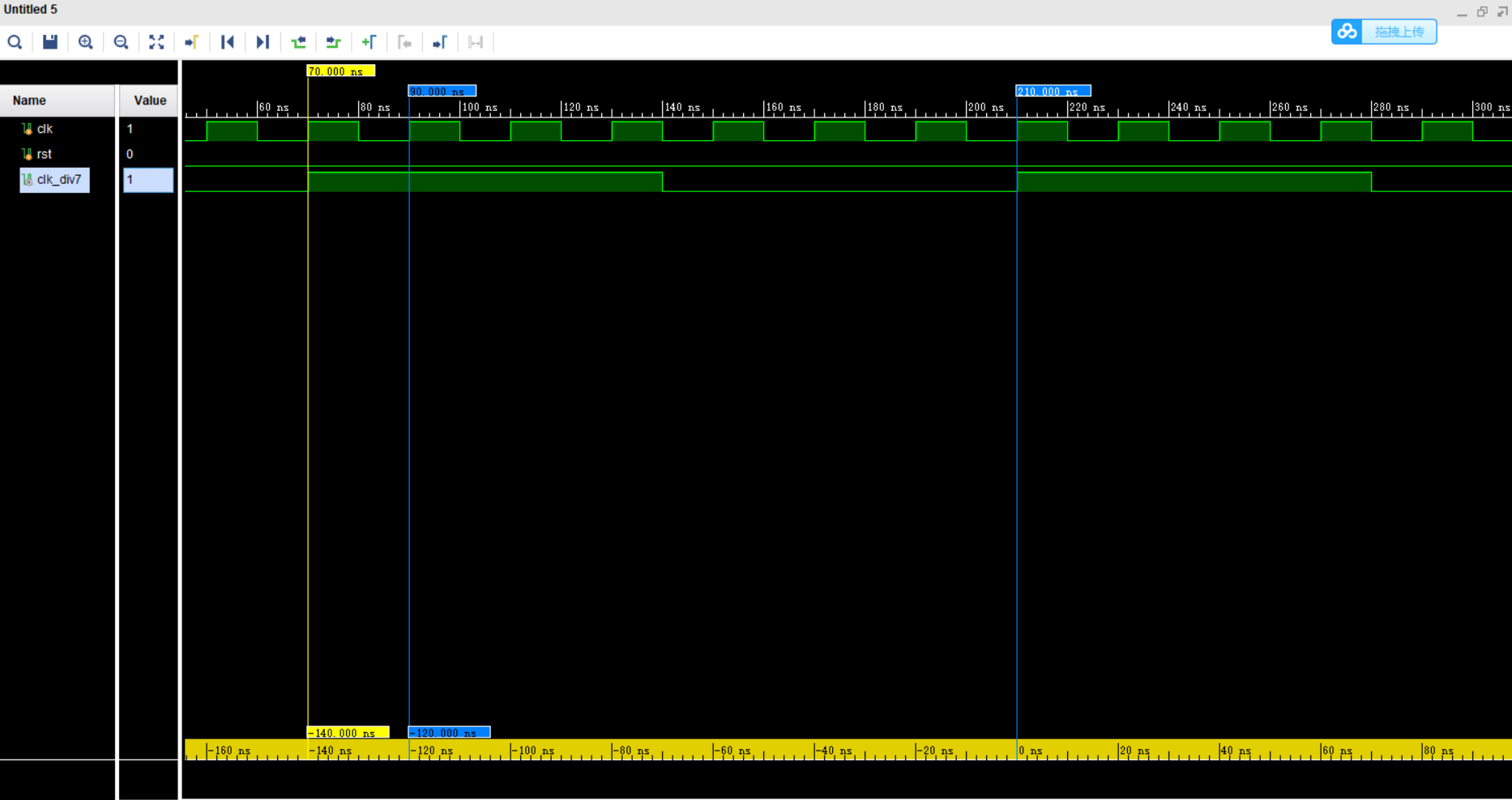

仿真波形如下:

可以看到,原时钟周期为20ns,分频后时钟周期为140ns。

N+0.5分频

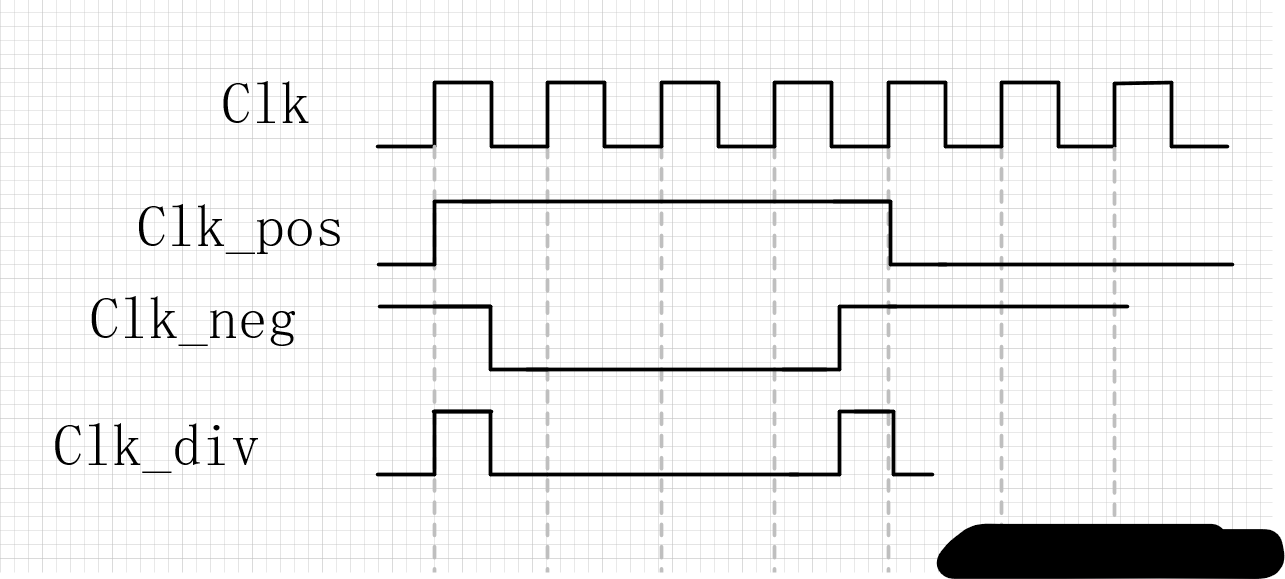

N+0.5分频需要时钟周期变为原来的N+0.5倍,因为有0.5出现,所以还是需要上升沿与下降沿一起用,以3.5分频为例,需要上升沿时钟和下降沿时钟按如下变化,然后相与。需要注意的占空比不是50%,一般小数分频丢不要求占空比。由下图可知,需要上升沿时钟拉高四个时钟周期,而下降沿始终需要拉低三个始终周期,前后各错开半个时钟周期。

代码如下:

module div_35(

input wire clk,

input wire rst,

output wire clk_div35

);

reg clk_pos,clk_neg;

reg [2:0] cnt_pos,cnt_neg;

always @(posedge clk or posedge rst) begin

if (rst) begin

// reset

cnt_pos <= 3'b000;

end

else if (cnt_pos == 3'b110) begin

cnt_pos <= 3'b000;

end

else begin

cnt_pos <= cnt_pos + 1'b1;

end

end

always @(posedge clk or posedge rst) begin

if (rst) begin

// reset

clk_pos <= 1'b0;

end

else if (cnt_pos == 3'b000) begin

clk_pos <= 1'b1;

end

else if(cnt_pos == 3'b100) begin

clk_pos <= 1'b0;

end

end

always @(negedge clk or posedge rst) begin

if (rst) begin

// reset

cnt_neg <= 3'b000;

end

else if (cnt_neg == 3'b110) begin

cnt_neg <= 3'b000;

end

else begin

cnt_neg <= cnt_neg + 1'b1;

end

end

always @(negedge clk or posedge rst) begin

if (rst) begin

// reset

clk_neg <= 1'b1;

end

else if (cnt_neg == 3'b000) begin

clk_neg <= 1'b0;

end

else if(cnt_neg == 3'b011) begin

clk_neg <= 1'b1;

end

end

assign clk_div35 = clk_pos & clk_neg;

endmoduletestbench:

module tb_35();

reg clk,rst;

wire clk_div35;

initial

begin

clk = 0;

rst = 1;

#5

rst = 0;

end

always #10 clk = ~clk;

div_35 inst(

.clk(clk),

.rst(rst),

.clk_div35(clk_div35));

endmodule

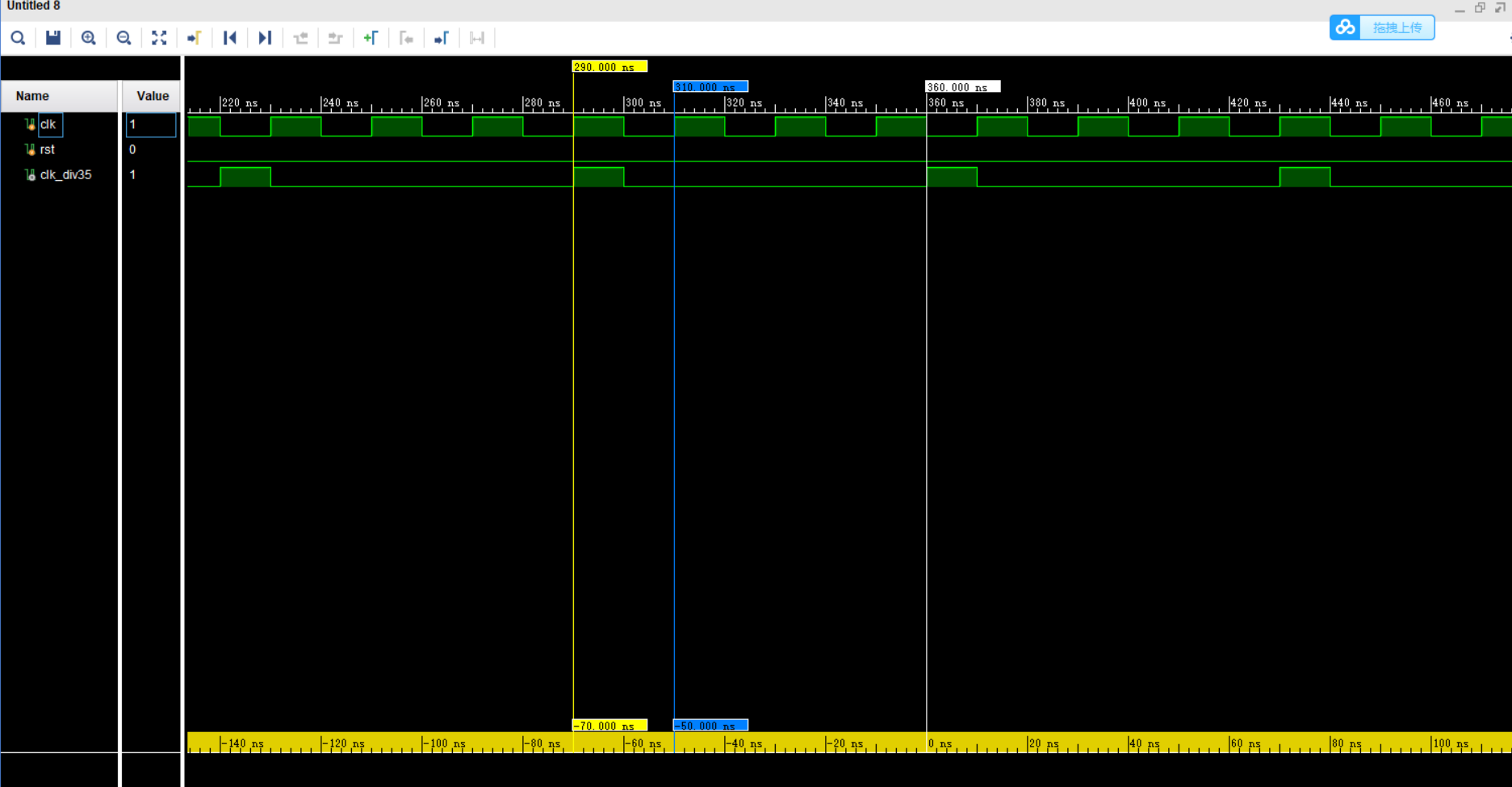

仿真波形图如下:

可以看到原时钟频率为20ns,分频后时钟频率为70ns。

任意小数分频

任意小数分频实现起来比较麻烦,首先需要确定分子和分母, 如5.3分频,5.3=53/10,53/10 =5...3,因此需要5(商)分频和8(余数+商)分频组合起来。然后解下面的方程组确定需要几个5分频,几个8分频。a+b=10,5a+8b=53;解得a=9,b=1,也就是说需要9个5分频和1个8分频。具体为什么这么做我也不是很懂,只把代码和结果贴在下面:

module div_53(

output reg clkout,

input rstn,

input refclk,

input [31:0] fenzi,//fenzi/fenmu must equal or more than 2

input [31:0] fenmu //fenzi/fenmu must equal or more than 2

);

reg [2:0] rstn_syn;

reg [31:0] cnt;

//1. reset synchronization;

//2. indicate that refclk is already stable

always @(posedge refclk) begin

rstn_syn[0] <= rstn;

rstn_syn[1] <= rstn_syn[0];

rstn_syn[2] <= rstn_syn[1];

end

//1. main algorithm

always @(posedge refclk or negedge rstn_syn[2]) begin

if(!rstn_syn[2]) cnt <= 0;

else begin

if(cnt < fenzi) cnt <= cnt + fenmu;

else cnt <= cnt + fenmu - fenzi;

end

end

//1. base the above algorithm, deduce clkout

always @(posedge refclk or negedge rstn_syn[2]) begin

if(!rstn_syn[2]) clkout <= 0;

else begin

if(((cnt > (fenzi>>1)) || (cnt == (fenzi>>1))) && (cnt < fenzi)) clkout <= 1;

else clkout <= 0;

end

end

endmoduletestbench:

module tb();

reg refclk;

initial begin

refclk = 0;

end

always #0.2 refclk = !refclk;

reg rstn;

initial begin

rstn = 0;

#100;

rstn = 1;

end

reg [31:0] fenzi;

reg [31:0] fenmu;

reg enable_clkFracDiv;

initial begin

fenzi=32'd53;

fenmu=32'd10;

enable_clkFracDiv=0;

#200;

enable_clkFracDiv=1;

end

div_5 clkFracDiv(

/*output reg */.clkout (clkout),

/*input */.rstn (rstn && enable_clkFracDiv ),

/*input */.refclk (refclk),

/*input [31:0] */.fenzi (fenzi ),//fenzi/fenmu must equal or more than 2

/*input [31:0] */.fenmu (fenmu ) //fenzi/fenmu must equal or more than 2

);

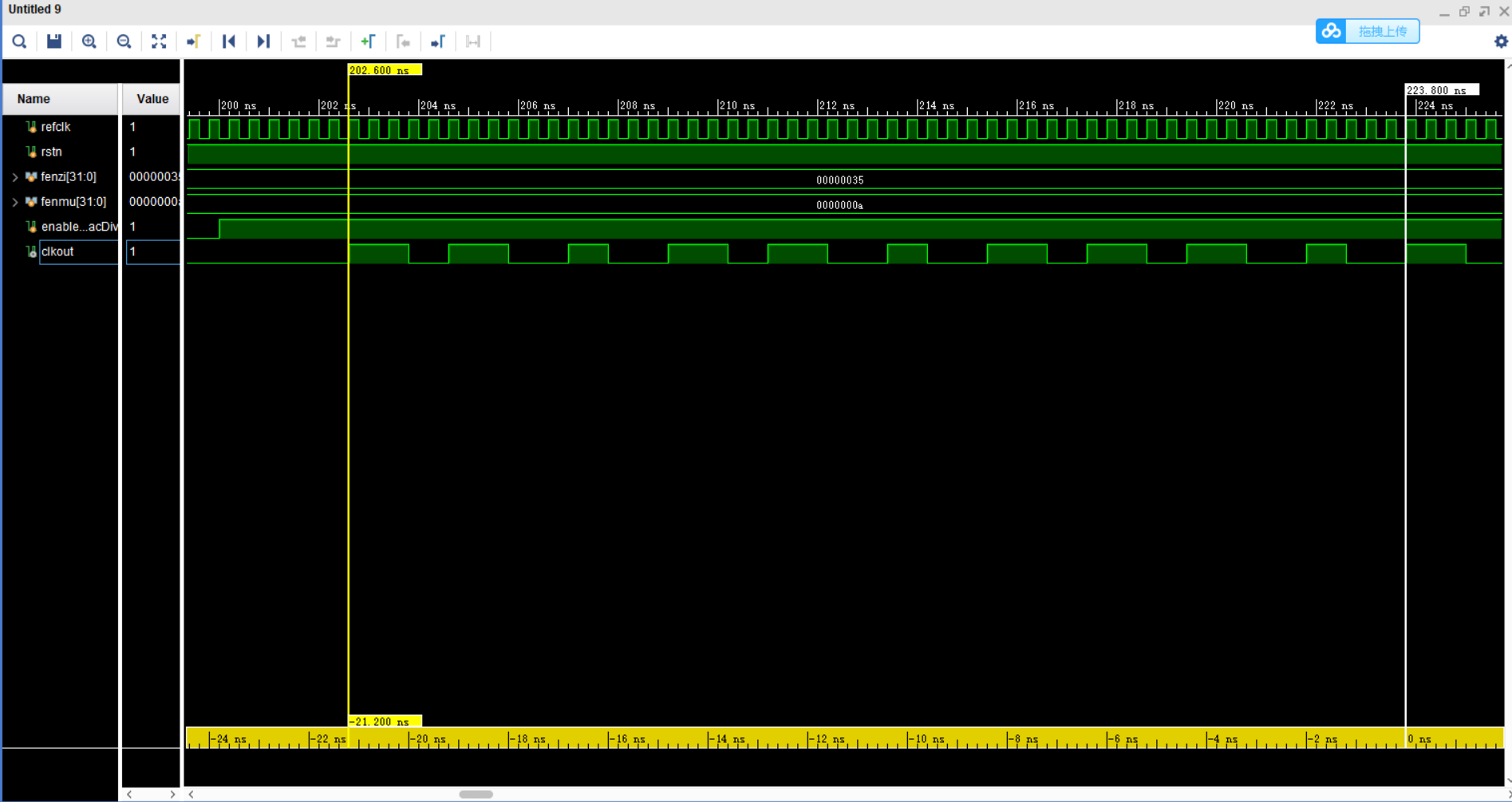

endmodule仿真波形如下:

虽然可以实现原时钟53个时钟,输出10个时钟,但会发生时钟周期抖动,并且并不是5分频和8分频组成的。不懂。

最后

以上就是暴躁太阳最近收集整理的关于分频电路的实现:奇数分频、偶数分频和小数分频偶数分频奇数分频N+0.5分频任意小数分频的全部内容,更多相关分频电路内容请搜索靠谱客的其他文章。

发表评论 取消回复