D触发器实现分频器

对于分频器的实现,我们最常用的方法就是通过计数器来实现,具体的实现可以看前面的文章,但是通过D触发器实现却很少遇到,我将通过这篇文章讲解D触发器实现分频器,这里以9分频为例。

我们要实现的是通过D触发器和组合逻辑实现占空比为50%的9分频电路,首先我们通过D触发器实现序列发生器,输出000001111循环序列,然后用下降沿的D触发器打一拍,将两个信号相或后输出即可。

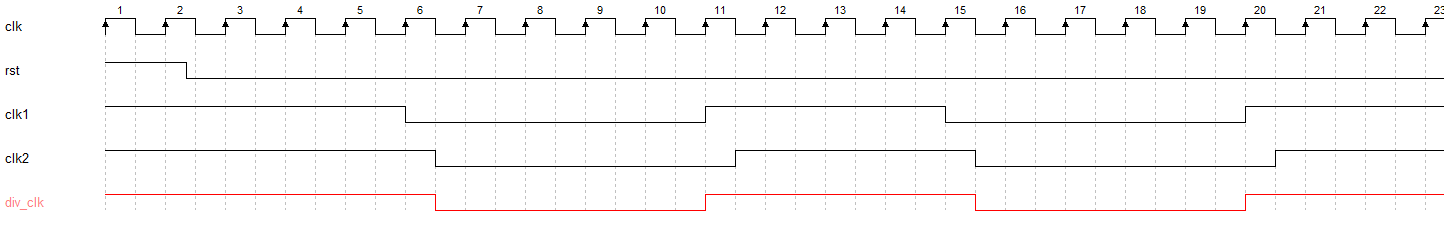

通过上面的思路,我们首先画出对应的波形图,其中clk1为序列发生器产生的序列脉冲,clk2是clk1在系统时钟clk的下降沿打一拍得到的信号,div_clk为我们得到的9分频信号。

现在的关键就在于如何产生000001111循环序列,因为该循环序列有9个状态,所以至少需要4个触发器,所以我们首先使用4个触发器列出对应的状态:

| Q3Q2Q1Q0 | D |

|---|---|

| 0000 | 1 |

| 0001 | 1 |

| 0011 | 1 |

| 0111 | 1 |

| 1111 | 0 |

| 1110 | 0 |

| 1100 | 0 |

| 1000 | 0 |

| 0000 ??? | 0 |

此时我们看到使用四个触发器时,我们在产生循环序列时,当产生第5个0时,发现触发器的取值和产生第一个1时的取值相同,所以,不能用四个触发器来产生该循环序列,为了满足条件,我们使用五个触发器,如下表:

| Q4Q3Q2Q1Q0 | D |

|---|---|

| 00000 | 1 |

| 00001 | 1 |

| 00011 | 1 |

| 00111 | 1 |

| 01111 | 0 |

| 11110 | 0 |

| 11100 | 0 |

| 11000 | 0 |

| 10000 | 0 |

| 00000 | 1 |

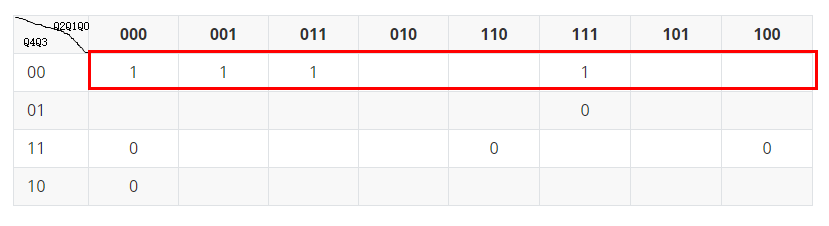

从上面可以看到,五个触发器可以满足条件,在确定了触发器的个数之后,我们就要通过上表来画出对应发的卡诺图,然后进行化简,得到状态方程,然后根据状态方程画出电路。对应的卡诺图如下:

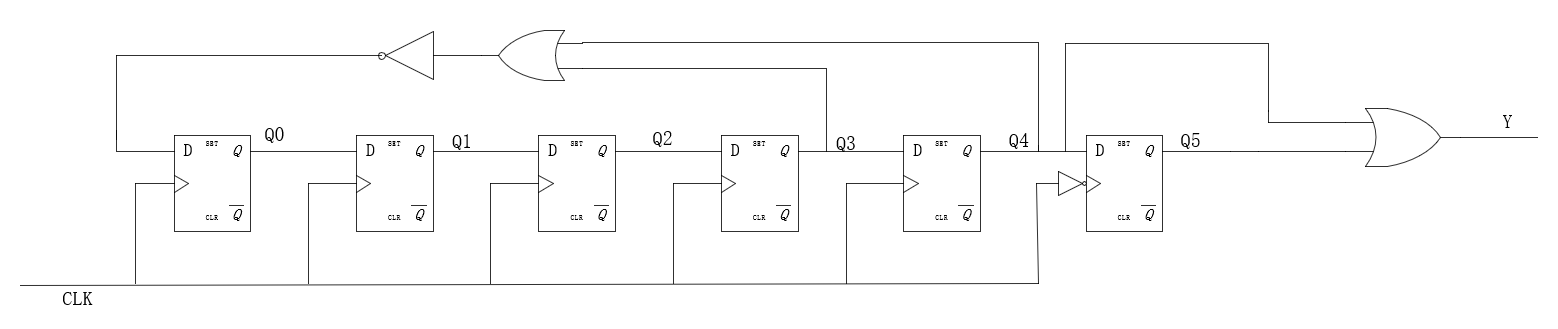

在化简的时候,没有数据的地方,我们既可以看做1,也可以看做0,最后的化简结果为D=Q4‘Q3’=(Q4+Q3)’,根据状态方程就可以设计电路图了,电路图如下:

得到电路图后,下面给出完整的代码:

// -----------------------------------------------------------------------------

// Copyright (c) 2014-2021 All rights reserved

// -----------------------------------------------------------------------------

// Author : dongtaolv

// Email : tdlv@stu.xidian.edu.cn

// File : div9_clk.v

// Create : 2021-04-27 11:46:24

// Revise : 2021-04-27 11:46:24

// Editor : sublime text3, tab size (4)

// -----------------------------------------------------------------------------

module div9_clk(

input wire clk,

input wire rst,

output wire div_clk

);

reg Q0,Q1,Q2,Q3,Q4;

wire D0;

reg out_reg;

always @(posedge clk)begin

if(rst)begin

Q0 <= 1'b0;

Q1 <= 1'b0;

Q2 <= 1'b0;

Q3 <= 1'b0;

Q4 <= 1'b0;

end

else begin

Q0 <= D0;

Q1 <= Q0;

Q2 <= Q1;

Q3 <= Q2;

Q4 <= Q3;

end

end

always @(negedge clk)begin

if(rst)begin

out_reg <= 1'b0;

end

else begin

out_reg <= Q4;

end

end

assign D0 = ~(Q3 | Q4);

assign div_clk = out_reg | Q4;

endmodule

tb文件如下:

// -----------------------------------------------------------------------------

// Copyright (c) 2014-2021 All rights reserved

// -----------------------------------------------------------------------------

// Author : dongtaolv

// Email : tdlv@stu.xidian.edu.cn

// File : tb_div9_clk.v

// Create : 2021-04-27 11:47:34

// Revise : 2021-04-27 11:47:34

// Editor : sublime text3, tab size (4)

// -----------------------------------------------------------------------------

`timescale 1ns/1ps

module tb_div9_clk;

reg clk;

reg rst;

wire div_clk;

initial begin

clk = 0;

rst = 1;

#100

rst = 0;

end

always #10 clk = ~clk;

div9_clk inst_div9_clk (

.clk(clk),

.rst(rst),

.div_clk(div_clk)

);

endmodule

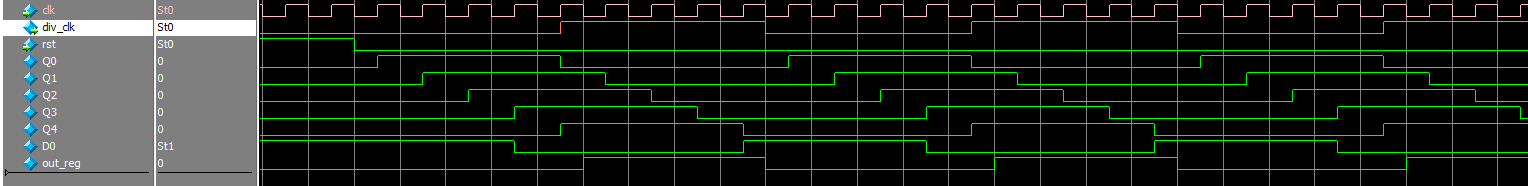

仿真图如下:

其中,clk为系统时钟,div_clk为9分频的时钟。

最后

以上就是昏睡金鱼最近收集整理的关于D触发器实现分频器的全部内容,更多相关D触发器实现分频器内容请搜索靠谱客的其他文章。

发表评论 取消回复