Ⅳ、数据选择器与分配器

一、数据选择器(MUX)

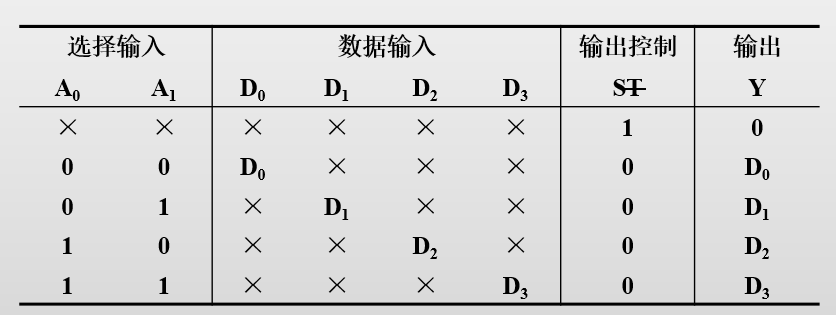

1、74LS153

双四选一多路选择器

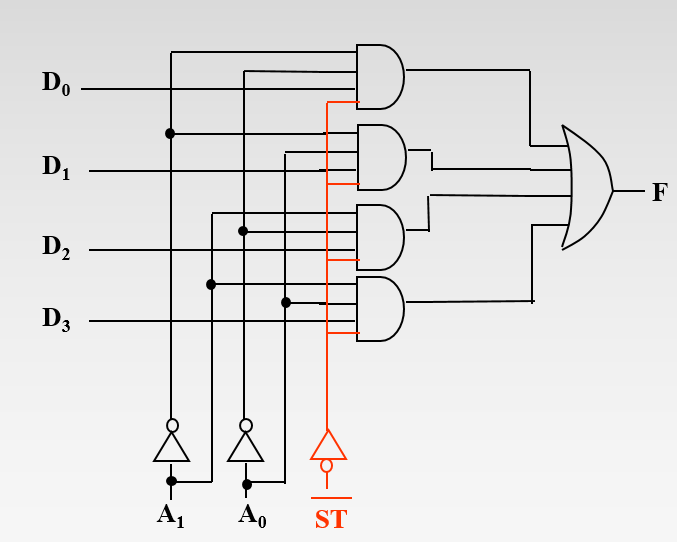

(1)、内部结构

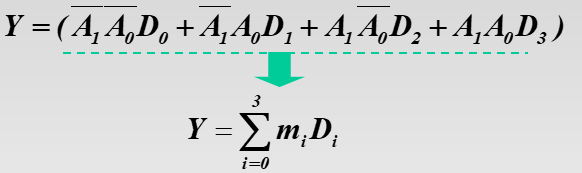

(2)、功能

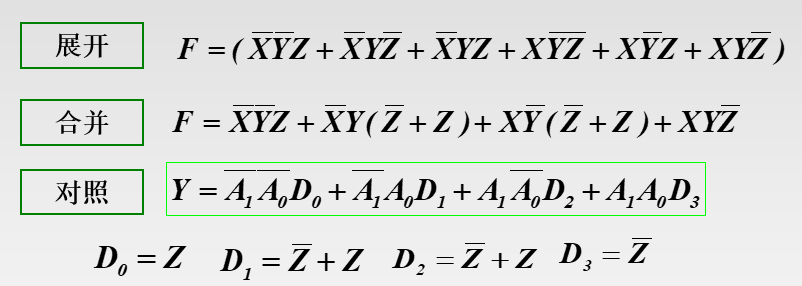

(3)、应用

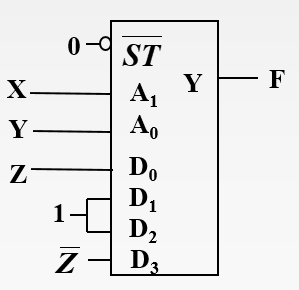

用四选一选择器实现函数F(X,Y,Z)=∑(1,2,3,4,5,6)

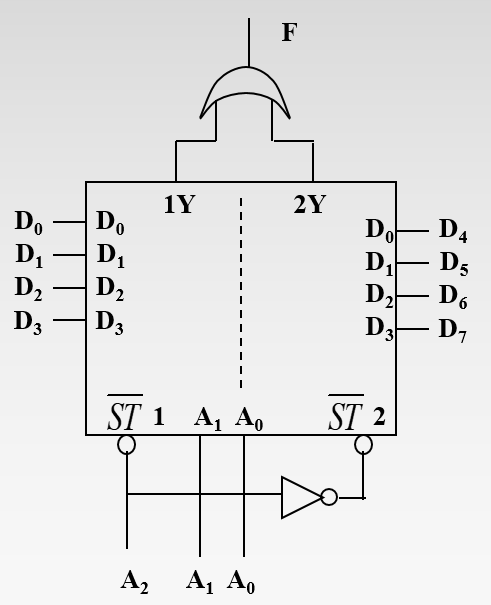

(4)、74LS15八选一

用两片74LS153实现

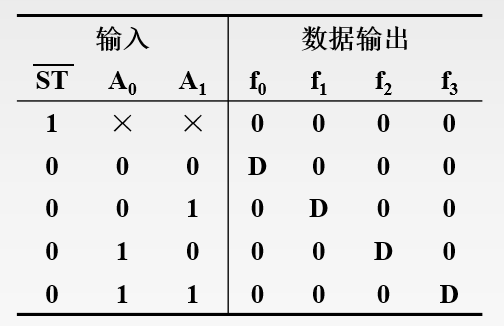

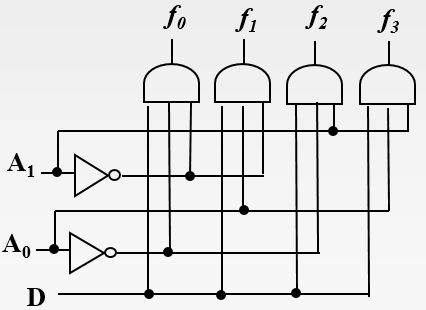

二、数据分配器

内部结构

Ⅴ、译码器和编码器

一、译码器

多输入多输出的组合逻辑部件。对具有特定含义的输入代码进行翻译,将其转换成相应的输出信号。

1、常用译码电路

二进制译码器

二-十进制译码器

数字显示译码器

(1)、二进制译码器

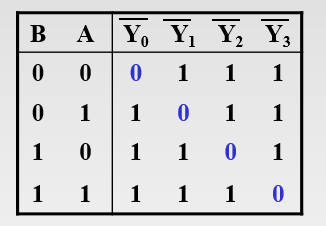

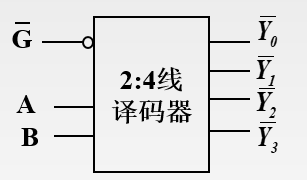

①、2:4译码器,74LS139

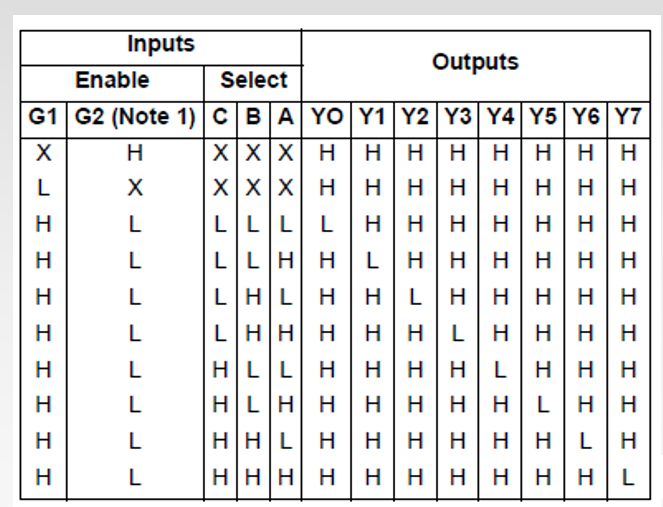

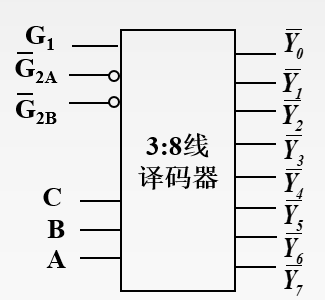

②、3:8译码器,74LS138

Note 1:G2=G2A+G2B

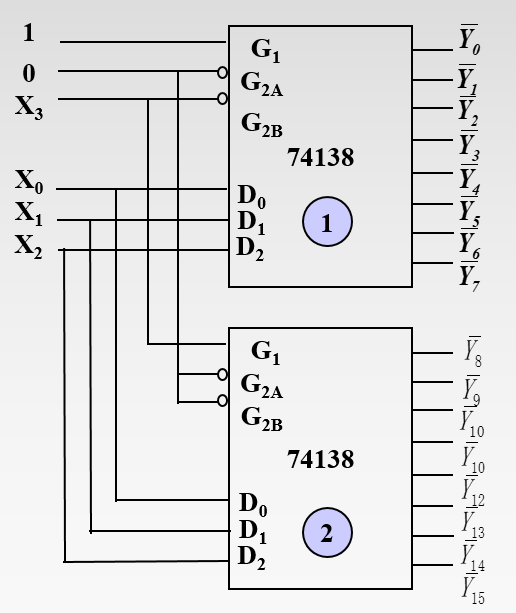

③、4:16译码器,74LS154

两片74LS138组成

使能端作用:

使输入端稳定后再送到输出端

拓展逻辑功能

2、二-十进制译码器

74LS42

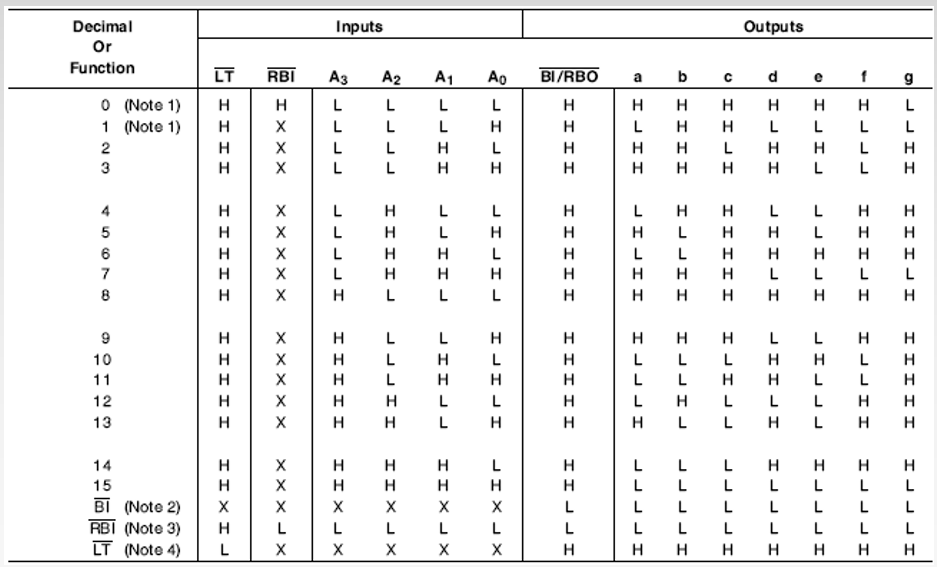

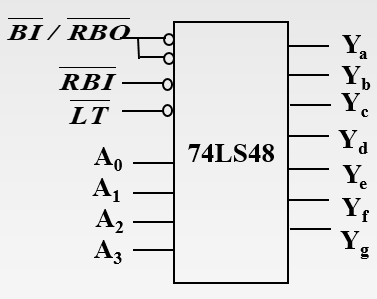

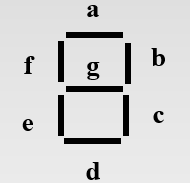

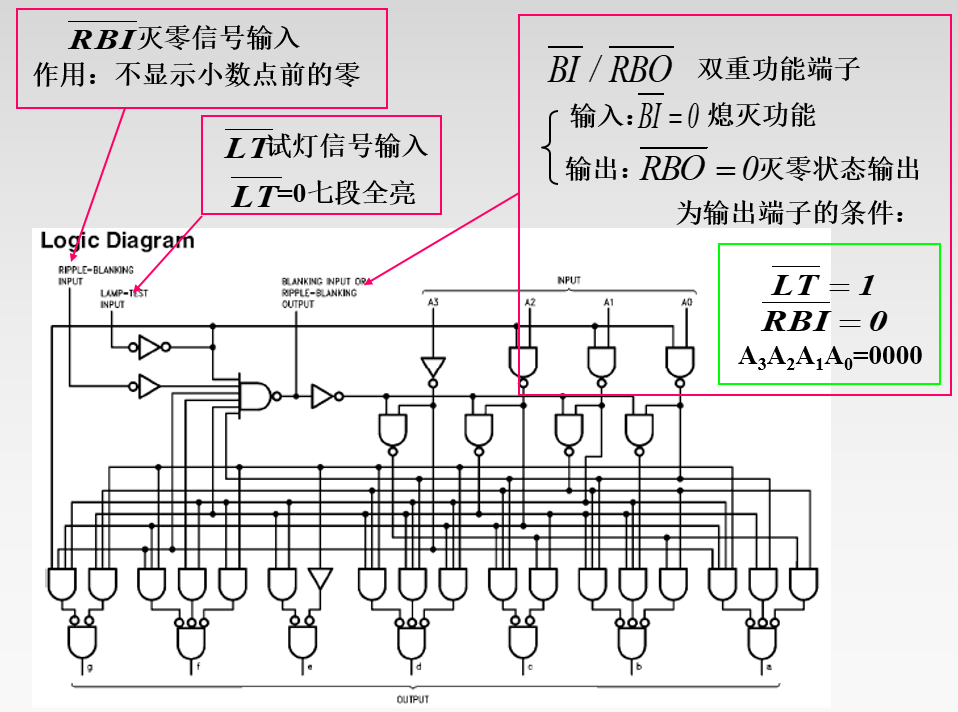

3、数字显示译码器

74LS48

作用:驱动七段发光二极管

二、编码器

将某种代码或电位信号转换成二进制码输出的电路

任意时刻只允许一个输入信号为有效信号

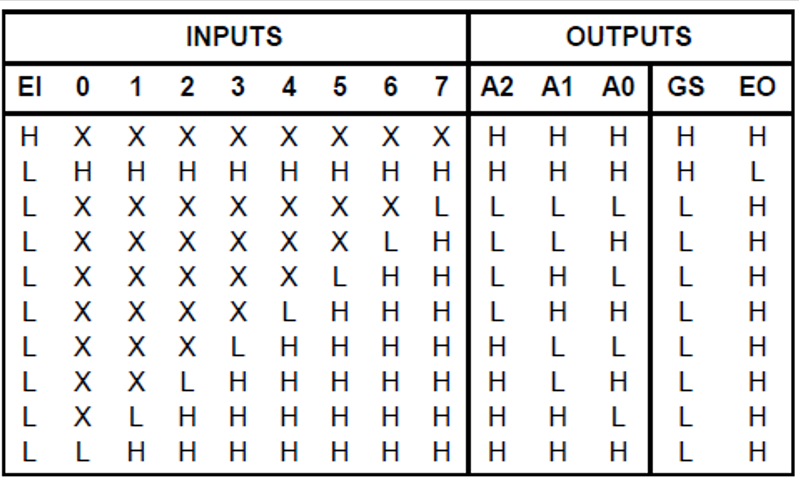

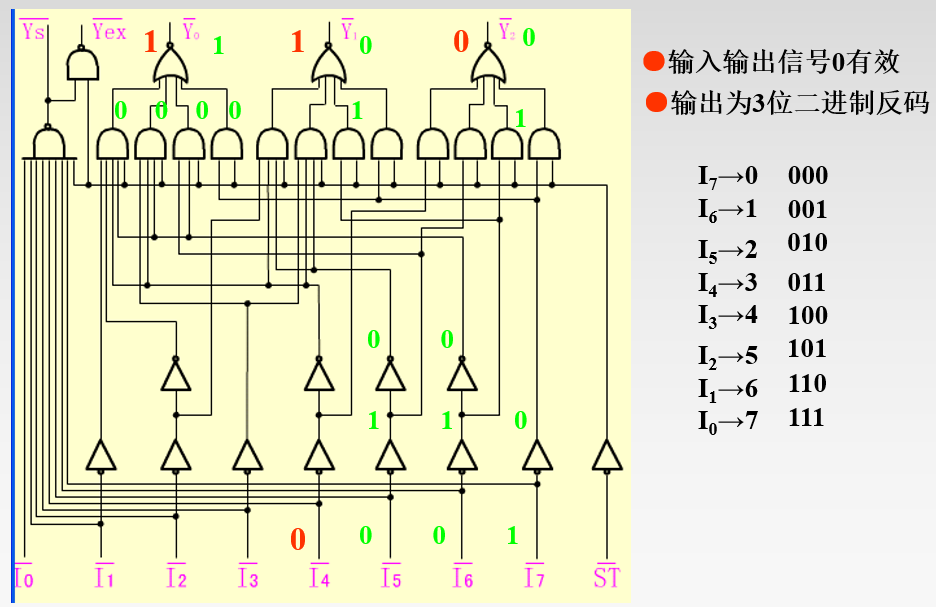

74LS148

具有优先级的编码器

实质:允许多个有效信号输入,输出只对优先级别高的信号编码

三、数据比较器与加法器

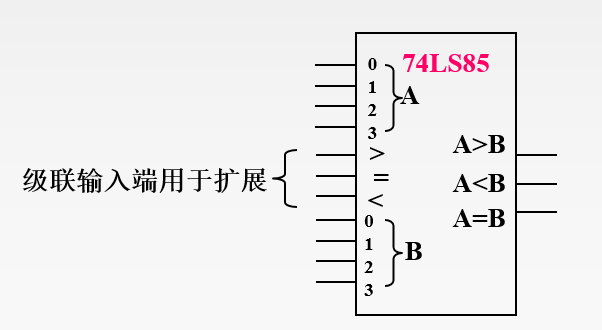

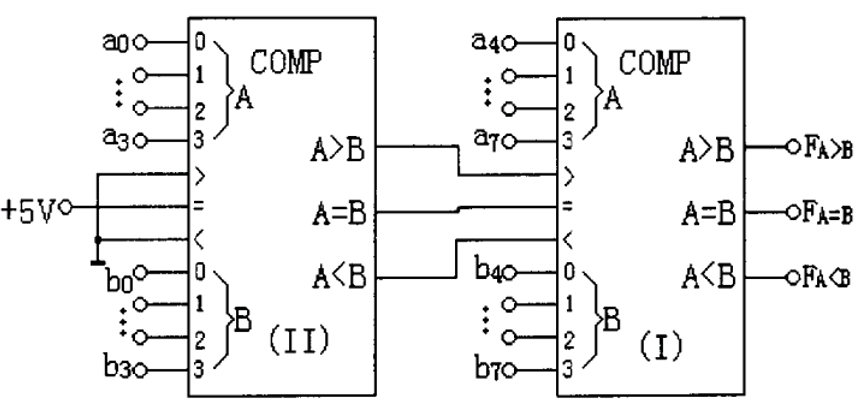

1、74LS85:四位比较器

两片74LS85构成八位数字比较器

2、加法器

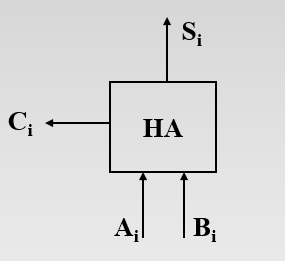

(1)、半加器

两个一位二进制数相加,并能向高位进位的逻辑电路

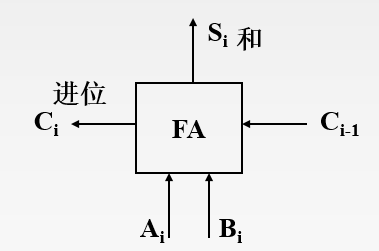

(2)、全加器

实现两个一位二进制数相加的同时,再加上低位进位的逻辑电路

Si=Ai⊕Bi⊕Ci-1

Ci=AiBi+(Ai⊕Bi)Ci-1

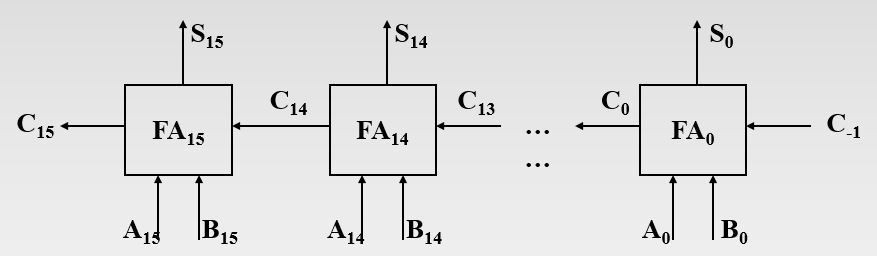

(3)、串行加法器

多个FA串行连接

问题:最终和的输出要等待进位的逐级上传,速度低

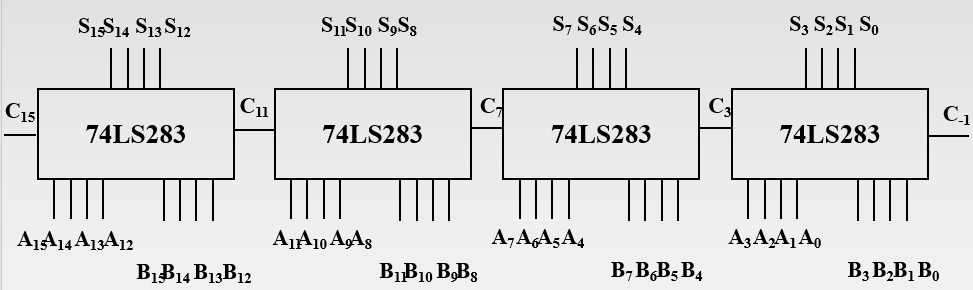

(4)、并行加法器

74LS283,四位超前进位并行加法器

将字长n位分成若干组,组内采用超前进位,组间采用串行进位

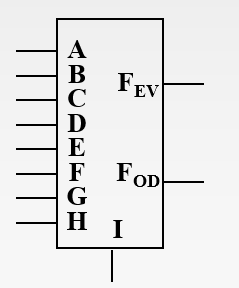

Ⅶ、奇偶校验器

奇校验:加上校验位使得1的个数为奇

偶校验:加上校验位使得1的个数为偶

74LS280

小结:

数据选择器:通过控制信号完成多选一

数据分配器:通过控制信号完成输入信号的分配

译码器:将给定的二进制编码转换成对应的输出信号

编码器:将给定信号转换成二进制编码

数据比较器:按位比较两串二进制数大小

加法器:完成加法

奇偶校验器:对二进制串进行校验,检测是否有错误

最后

以上就是沉默洋葱最近收集整理的关于组合逻辑2的全部内容,更多相关组合逻辑2内容请搜索靠谱客的其他文章。

发表评论 取消回复