目录

- 1. 题目

- 2. 代码

- 2.1 DUT

- 2.2 TB

- 3. 仿真

- 4. 小结

1. 题目

写一个组合逻辑代码,可以直接输出以2为底的对数值,向上取整。

2. 代码

这个代码主要是用来熟悉for循环的使用,取以2为底的对数,通过右移实现。

2.1 DUT

module log(

input wire [31:0] in,

//input wire clk,

//input wire rst_n,

output wire [7:0] out

);

// 方案一

function integer clogb2 (input integer bit_depth);

begin

for(clogb2=0; bit_depth>0; clogb2=clogb2+1)

bit_depth = bit_depth>>1;

end

endfunction

assign out = clogb2(in-1'b1);

// 方案二

integer i;

reg [31:0] bit_reg;

integer bit_tmp;

always @(*) begin

bit_reg = in-1'b1;

for (i=0; bit_reg > 0; i=i+1) begin

bit_reg = bit_reg >> 1'b1;

end

en

endmodule : log

2.2 TB

module tb_log();

reg [31:0] in;

reg clk, rst_n;

wire [7:0] out;

initial begin

in = 'd4;

#20

in = 'd8;

#20

in = 'd16;

#20

in = 'd32;

#20

in = 'd10;

#20

in = 'd17;

#2000

$finish;

end

log dut(

in,

out

);

initial begin

$fsdbDumpfile("tb_log.fsdb");

$fsdbDumpvars(0, tb_log);

$fsdbDumpon;

end

endmodule : tb_log

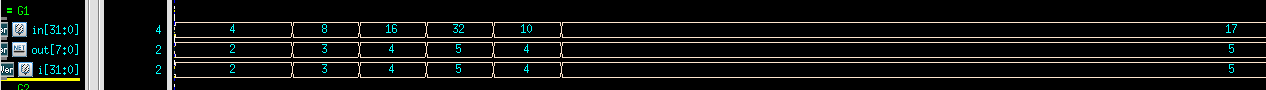

3. 仿真

4. 小结

通过方案二我们可以发现,在组合逻辑当中for循环的先后是可以有一定的先后顺序的,并不是像generate for一样,直接并行展开,这也许和采用阻塞赋值有一定的关系,如果方案二采用非阻塞赋值,可能for循环不能结束。方案一则需要注意function的使用,至少有一个输入,但是没有输出;不能包含always语句和时间控制语句;可以有返回值。

最后

以上就是乐观草莓最近收集整理的关于verilog编程题-取对数1. 题目2. 代码3. 仿真4. 小结的全部内容,更多相关verilog编程题-取对数1.内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复