时序逻辑电路设计描述技巧

目录

时序逻辑电路设计描述技巧

9.1、时序逻辑电路的特点和基本单元

(1)特点

(2)基本存储单元

9.2、常见时序逻辑电路的描述

(1)计数器

(2)时钟分频器

(3)通用移位寄存器

(4)线性反馈移位寄存器——LFSR建模

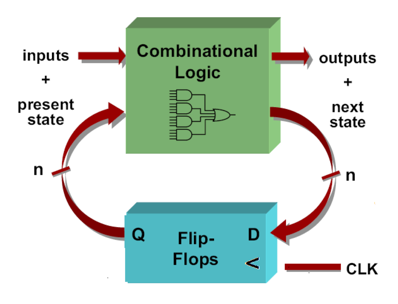

与组合逻辑电路不同,时序逻辑电路的输出不仅与当前的输入有关,还与电路原来的状态有关,有组合逻辑和存储电路、或仅由存储电路组成。

9.1、时序逻辑电路的特点和基本单元

| 一般时序电路的结构 |

|

|

(1)特点

记忆特性是时序逻辑电路的基本特征。

时序逻辑电路一般分为同步时序电路和异步时序电路两类。同步时序电路中所有存储单元状态变化都由同一时钟信号控制,比较容易满足建立时间和保持时间的要求,可以很好地避免电路中的毛刺,有利于器件移植和进行静态序分析(STA)。而异步时序电路不存在全局时钟,各触发器翻转的时间不定,数据传输效率较低,电路的核心由组合逻辑实现,最大的问题是容易产生毛刺,容易影响电路可靠性、稳定性。因此同步时序电路可以获得比异步时序电路更高的工作可靠性和工作速度,设计复杂度远远低于异步时序电路。

一般的综合工具不支持异步时序逻辑的综合,并且用异步时序逻辑很难控制由组合逻辑和延迟所产生的冒险和竞争。

(2)基本存储单元

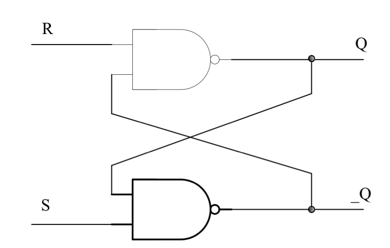

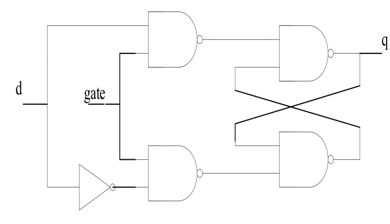

时序逻辑电路包含存储电路,存储电路是通过基本的存储单元来实现的。存储单元按触发方式可以分为电平触发和边沿触发两种。电平触发实现的是锁存器,边沿触发实现的是触发器。

①锁存器是电平触发的存储单元,基本的锁存器是RS锁存器,使用交叉耦合连接的或非门与非门反馈结构使得电路保存0、1状态,但这种与非门结构的RS锁存器,某些情况输出不稳定,输入为00变为11时会在电路中产生竞争,一般使用经过改进的RS锁存器,即透明锁存器。

|

|

|

| RS锁存器 | 透明锁存器 |

| Module latch(d,gate,q); Input d, gate; Output q; Wire d,gate; Reg q; Always @ (d or gate) If(gate) q <= d ; endmodule | |

需要谨慎使用Latch:

- 同步时序设计中要慎用latch,一般使用触发器实现同步时序设计,便于后端时序分析,插入扫描链;

- 低功耗设计中常会用到基于latch的门控时钟电路;

- 通过综合工具的综合报告可发现无意生成的latch。

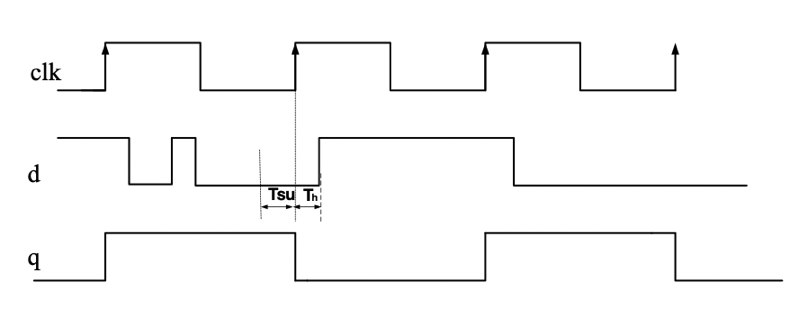

②触发器是边沿敏感的存储单元,数据的存储动作由某一信号(时钟)的上升沿或下降沿进行同步,所存储数据取决于时钟在其有效沿发生跳变时数据输入端当前的数据,其他时候数据保持不变。

触发器要正常工作必须满足两个重要参数:建立时间tsu和保持时间th。建立时间tsu是输入数据被锁存到触发器之前必须保持稳定不变的最小时间,保持时间th是指有效时钟沿到来之后,输入数据必须保持稳定不变的最小时间。如果不满足这两个参数,触发器就不能被正确置位,电路就不能正常工作。

|

|

| 触发器的建立时间和保持时间 |

触发器有两种复位方式,一种是同步复位,一种是异步复位。具体描述方式是:描述同步复位方式的always语句的事件敏感表中只有时钟的上升沿或下降沿信号,如always@(posedge clk)或always@(negedge clk);而异步复位方式还需要在always敏感列表中再加入复位信号,如always@(posedge clk or negedge reset)。

同步复位仅在时钟的有效沿采样复位信号,可有效避免因复位信号毛刺造成的亚稳态和错误,增强了电路的稳定性,可设计出100%的同步时序电路,有利于时序分许,其综合结果的频率往往较高。但使用同步复位时,复位信号长度大于时钟周期才能保证可靠复位,而且常会增加逻辑资源。

而异步复位作用时与时钟信号无关,如果异步复位释放时间与时钟有效沿达到时间一致,容易造成触发器输出亚稳态;另外如果产生异步复位信号的组合逻辑产生了毛刺,则毛刺的有效沿会使触发器误复位。但异步设计简单,节约逻辑资源。

9.2、常见时序逻辑电路的描述

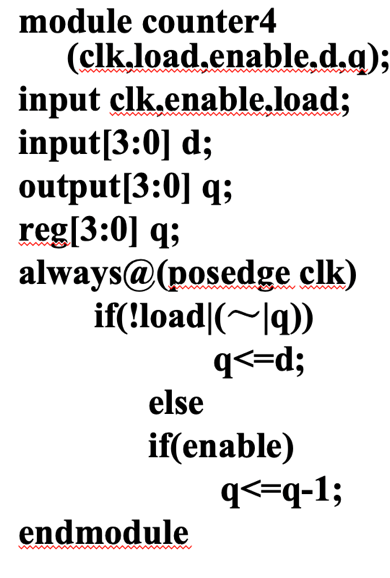

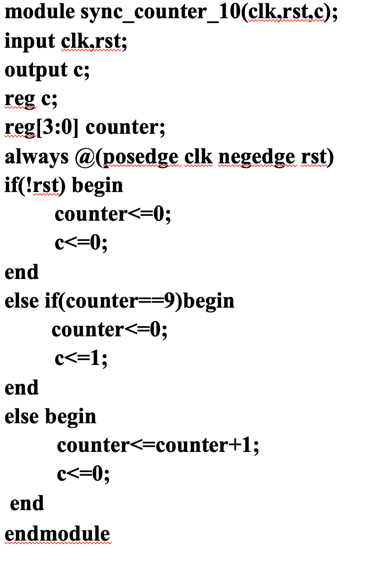

(1)计数器

计数器一般完成计数、定时、时钟分频和某些时序控制信号的生成,同步计数器最简单、直观的描述方式是用“+”或“-”常数的算术操作,最终对用的硬件由加法器(或减法器逻辑)和寄存器实现。

|

|

|

| 带使能端的同步置位递减计数器 | 同步十进制加法计数器 |

(2)时钟分频器

时钟分频器分为偶数分频器和奇数分频器。偶数分频器比较简单,只需实现一个时钟同步计数器,然后在响应的寄存器位抽头即可,奇数分频器稍微复杂,需使用case结构或简单的状态机,其难点在于如何通过组合逻辑调整分频时钟的占空比。(如果要获得50%占空比的分频时钟,需使用时钟正负沿。)

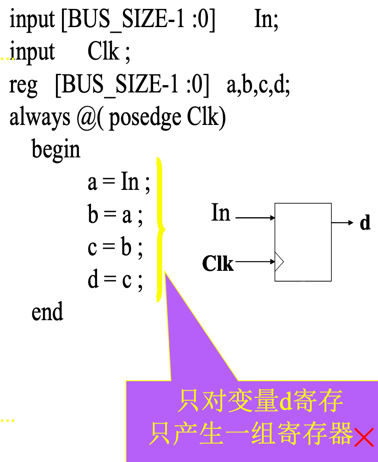

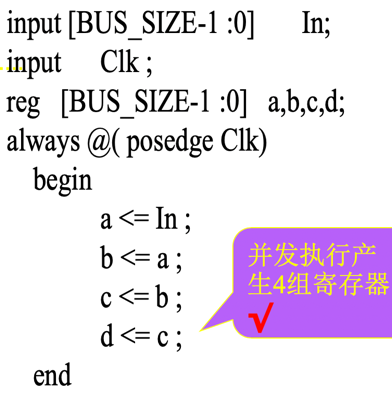

(3)通用移位寄存器

|

|

|

| 4位串行移位寄存器的两种描述 | |

(4)线性反馈移位寄存器——LFSR建模

线性反馈移位寄存器(Linear Feedback Shift Register,LFSR)是一种特殊的时序移位寄存器,能利用组合反馈逻辑生成相应的伪随机二进制序列。典型应用如计数器、伪随机数产生器、数据压缩、数据加解密、数据完整性检查等,相同的功能如果使用LFSR实现,面积和速度上都有明显优势。

n位LFSR是由n个触发器构成的寄存器链和链中某些节点的组合反馈回路组成。反馈回路逻辑选择异或门、同或门,每个寄存器仅实现时钟沿移位功能。根据反馈电路的不同,LFSR的实现结构分为内异或结构和外异或结构。

|

|

| n位内异或LFSR结构(也称一对多结构) |

|

|

| n位外异或LFSR结构(也称多对一结构) |

最后

以上就是乐观草莓最近收集整理的关于9、时序逻辑电路设计描述技巧时序逻辑电路设计描述技巧的全部内容,更多相关9、时序逻辑电路设计描述技巧时序逻辑电路设计描述技巧内容请搜索靠谱客的其他文章。

发表评论 取消回复